Datasheet Summary

( DataSheet : .. )

CLA80000 Series

High Density CMOS Gate Arrays

DS3820

ISSUE 2.1

July 1997

INTRODUCTION

The CLA80k gate array series from Zarlink Semiconductor offers advantages in speed and density over previous array series. Improvements in design bined with advances in simulation accuracy allow the implementation of plex systems in excess of 260,000 gates.

ARRAY SIZES

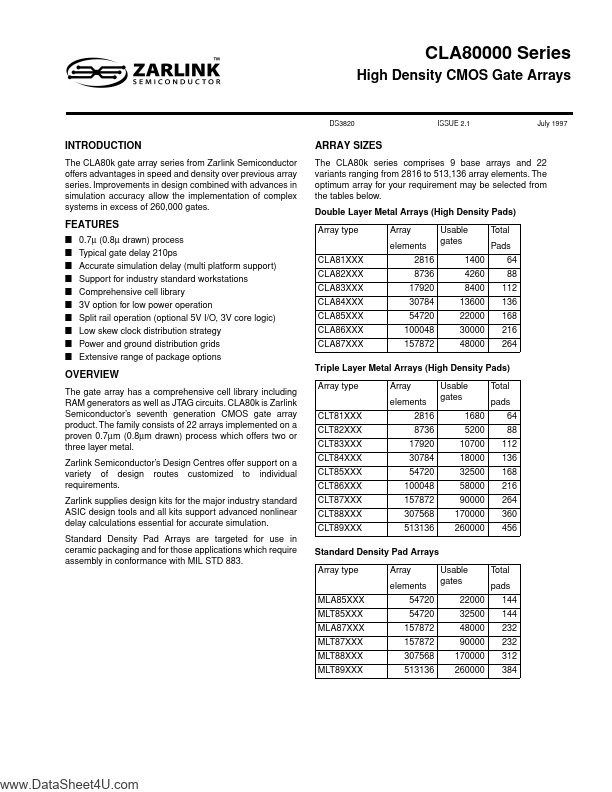

The CLA80k series prises 9 base arrays and 22 variants ranging from 2816 to 513,136 array elements. The optimum array for your requirement may be selected from the tables below. Double Layer Metal Arrays (High Density Pads) Array type CLA81XXX CLA82XXX CLA83XXX CLA84XXX CLA85XXX CLA86XXX...