SP8400 Overview

Key Specifications

Key Features

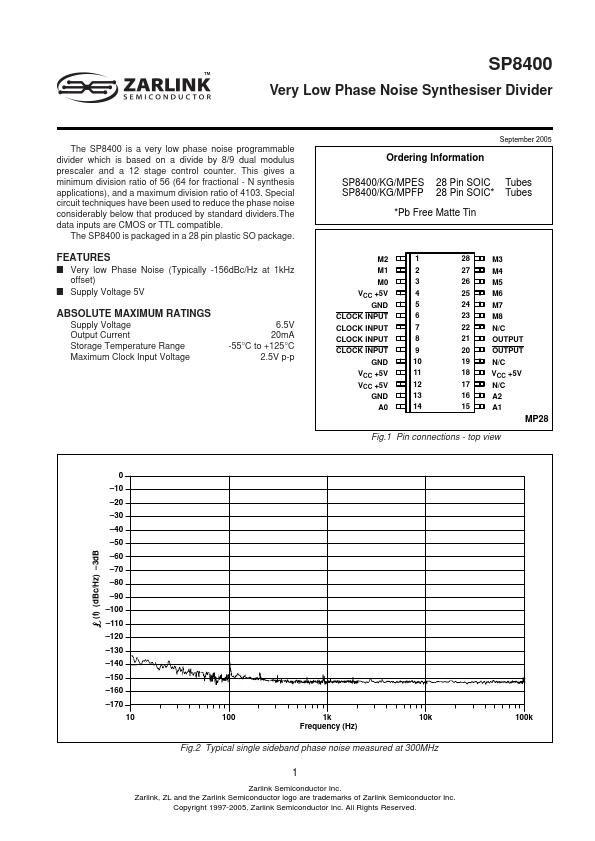

- N synthesis applications), and a maximum division ratio of 4103. Special circuit techniques have been used to reduce the phase noise considerably below that produced by standard data inputs are CMOS or TTL compatible. The SP8400 is packaged in a 28 pin plastic SO package

- 50 (f) (dBc/Hz)