ZL30121

Key Features

- Programmable output synthesizers generate clock frequencies from any multiple of 8 kHz up to 77.76 MHz in addition to 2 kHz

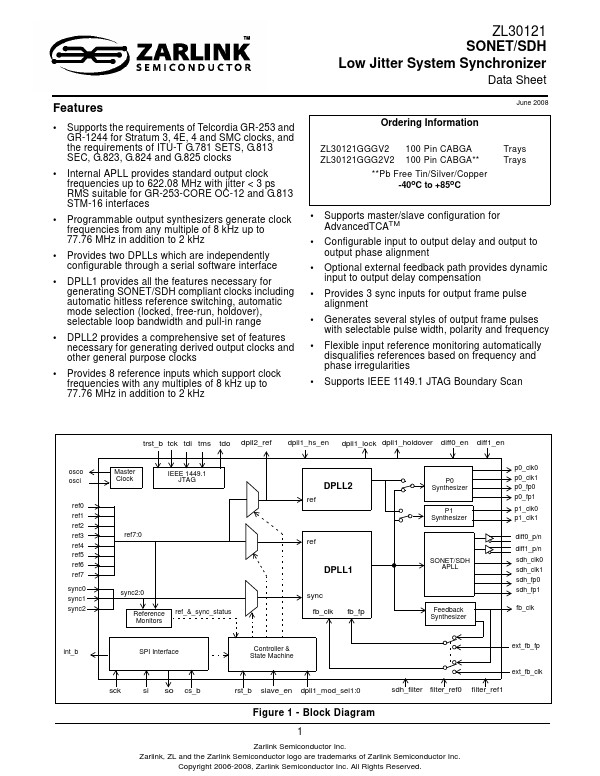

- Provides two DPLLs which are independently configurable through a serial software interface

- DPLL2 provides a prehensive set of features necessary for generating derived output clocks and other general purpose clocks

- Provides 8 reference inputs which support clock frequencies with any multiples of 8 kHz up to 77.76 MHz in addition to 2 kHz

Applications

- AdvancedTCATM Systems