74AC11112

74AC11112 is DUAL J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS manufactured by Texas Instruments.

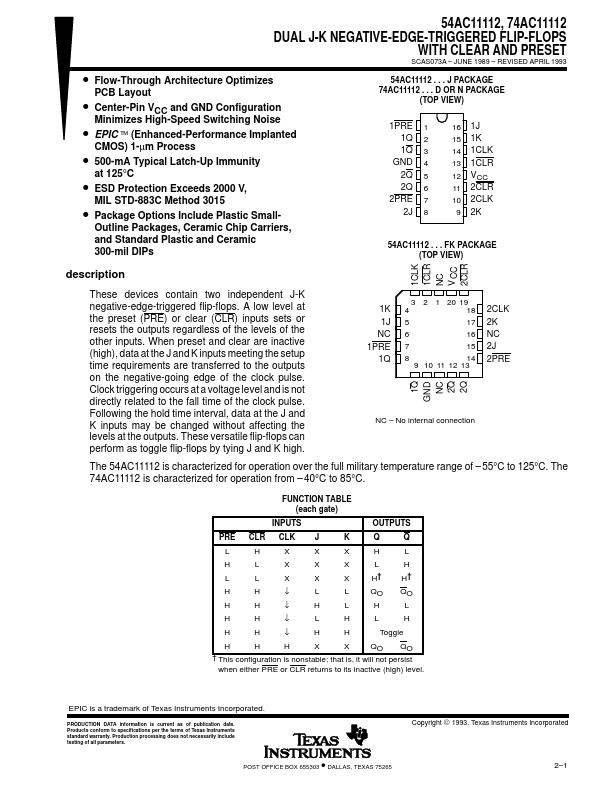

54AC11112, 74AC11112 DUAL J-K NEGATIVE-EDGE-TRIGGERED FLIP-FLOPS

WITH CLEAR AND PRESET

SCAS073A

- JUNE 1989

- REVISED APRIL 1993

- Flow-Through Architecture Optimizes

PCB Layout

- Center-Pin VCC and GND Configuration

Minimizes High-Speed Switching Noise

- EPIC ™ (Enhanced-Performance Implanted

CMOS) 1-µm Process

- 500-mA Typical Latch-Up Immunity at 125°C

- ESD Protection Exceeds 2000 V,

MIL STD-883C Method 3015

- Package Options Include Plastic Small-

Outline Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic

300-mil DIPs

54AC11112 . . . J PACKAGE 74AC11112 . . . D OR N PACKAGE

(TOP VIEW)

1PRE 1Q 1Q

GND 2Q 2Q

2PRE 2J

1 2 3 4 5 6 7 8

16 1J 15 1K 14 1CLK 13 1CLR 12 VCC...