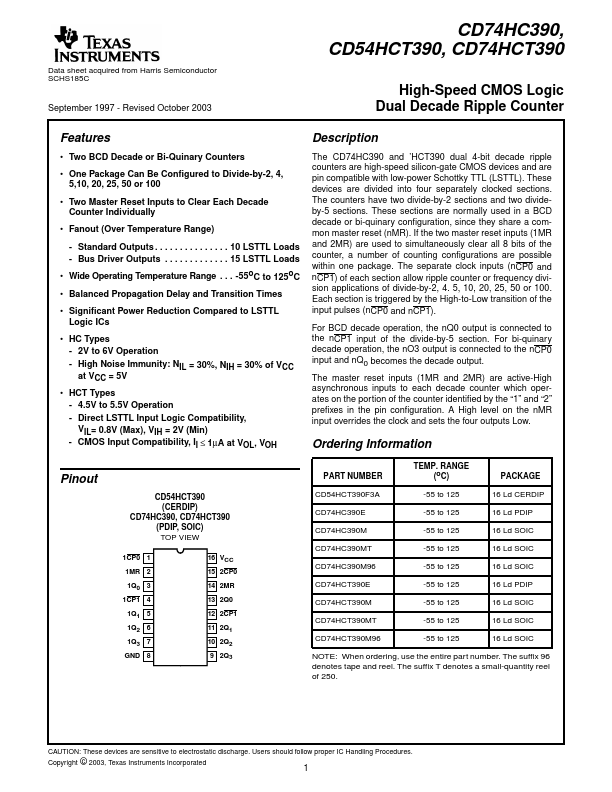

74HCT390 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 5 V

Description

Two BCD Decade or Bi-Quinary Counters - One Package Can Be Configured to Divide-by-2, 4, 5,10, 20, 25, 50 or 100 - Two Master Reset Inputs to Clear Each Decade Counter Individually - Fanout (Over Temperature Range) - Standard Outputs. Wide Operating Temperature Range.