ADS6424

FEATURES

- 12-Bit Resolution With No Missing Codes

- Simultaneous Sample and Hold

- 3.5d B Coarse Gain and upto 6d B

Programmable Fine Gain for SFDR/SNR Trade Off

- Serialized LVDS Outputs With Programmable Internal Termination Option

- Supports Sine, LVCMOS, LVPECL, LVDS Clock Inputs and Amplitude down to 400 m VPP

- Internal Reference With External Reference Support

- No External Decoupling Required for References

- 3.3-V Analog and Digital Supply

- 64 QFN Package (9 mm × 9 mm)

- Pin patible 14-Bit Family (ADS644X SLAS531A)

- Feature patible Dual Channel Family (ADS624X

- SLAS542A, ADS622X

- SLAS543A)

APPLICATIONS

- Base-station IF Receivers

- Diversity Receivers

- Medical Imaging

- Test Equipment

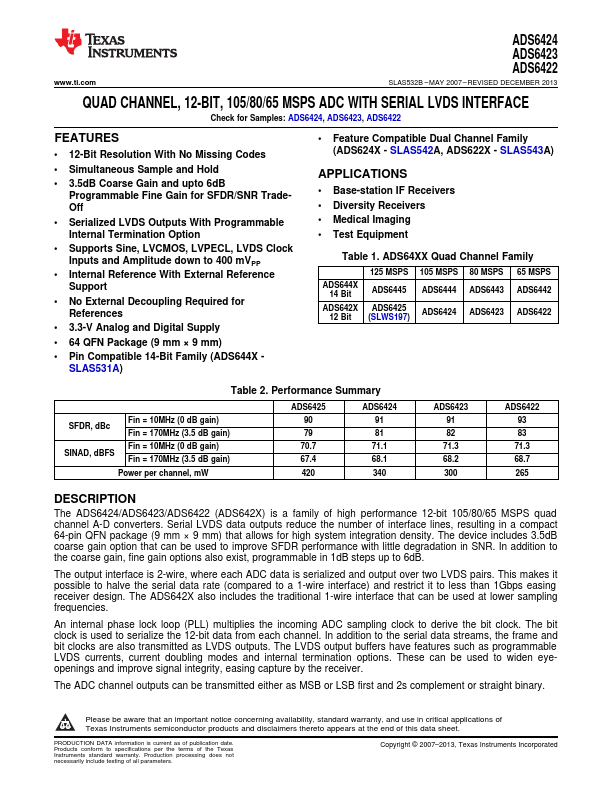

Table 1. ADS64XX Quad Channel Family

ADS644X 14 Bit

ADS642X 12 Bit

125 MSPS

ADS6445

ADS6425 (SLWS197)

105 MSPS ADS6444 ADS6424

80 MSPS ADS6443 ADS6423

65 MSPS ADS6442 ADS6422

Table 2. Performance Summary

SFDR, d Bc

Fin = 10MHz (0 d B gain) Fin = 170MHz (3.5 d B gain)

Fin = 10MHz (0...