CD74HC107

CD74HC107 is Dual J-K Flip-Flop manufactured by Texas Instruments.

Data sheet acquired from Harris Semiconductor SCHS139D

March 1998

- Revised October 2003

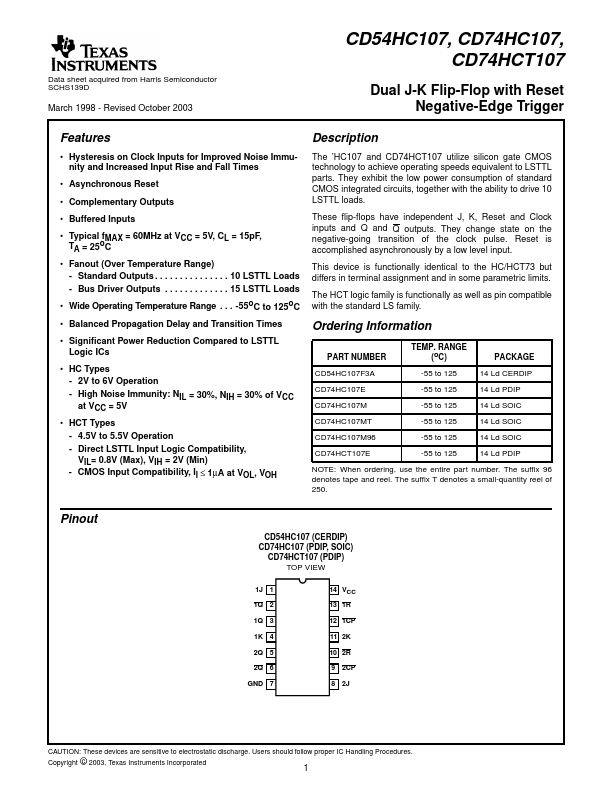

CD54HC107, CD74HC107, CD74HCT107

Dual J-K Flip-Flop with Reset Negative-Edge Trigger

[ /Title (CD74 HC107 , CD74 HCT10 7) /Subject (Dual J-K FlipFlop with Reset Negative-

Features

Description

- Hysteresis on Clock Inputs for Improved Noise Immunity and Increased Input Rise and Fall Times

- Asynchronous Reset

- plementary Outputs

- Buffered Inputs

- TTAyp=ic2a5lofCMAX = 60MHz at VCC = 5V, CL = 15pF,

- Fanout (Over Temperature Range)

- Standard Outputs

- -

- 10 LSTTL Loads

- Bus Driver Outputs

- - . . . 15 LSTTL Loads

- Wide Operating Temperature Range . ....