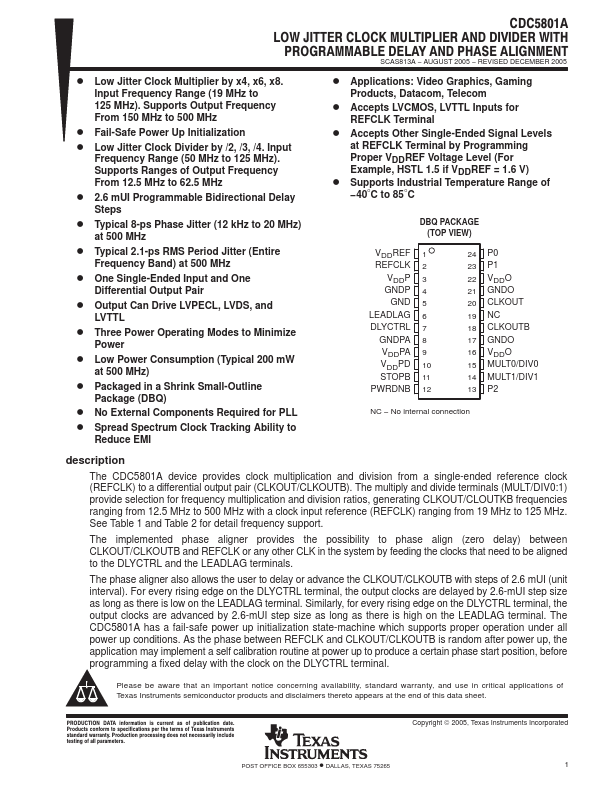

CDC5801A Overview

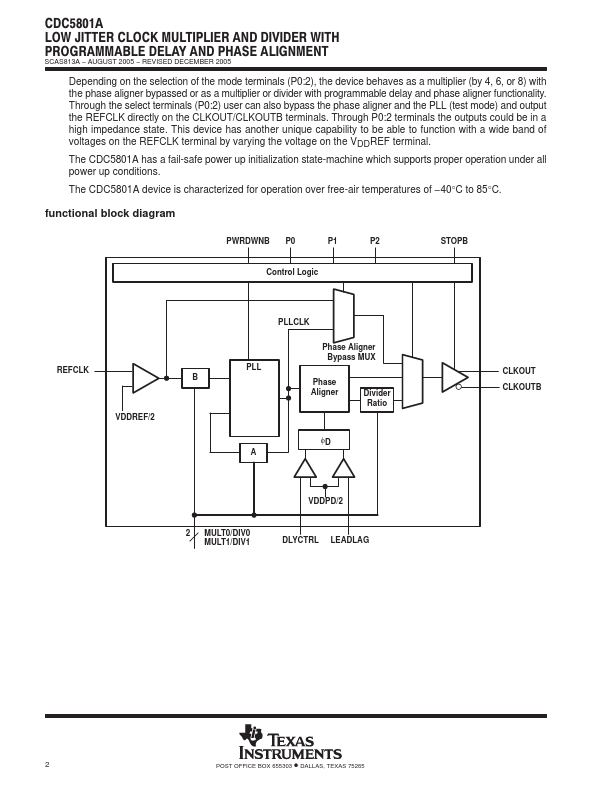

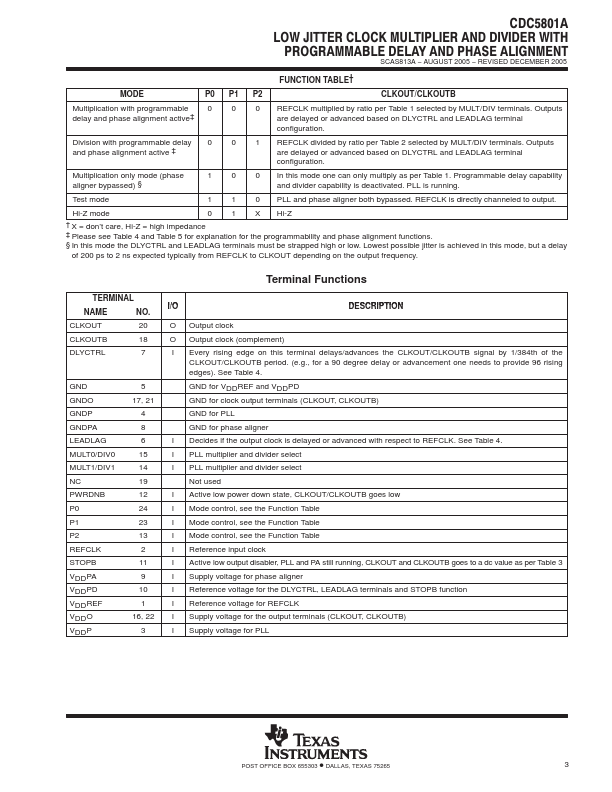

The CDC5801A device provides clock multiplication and division from a single-ended reference clock (REFCLK) to a differential output pair (CLKOUT/CLKOUTB). The multiply and divide terminals (MULT/DIV0:1) provide selection for frequency multiplication and division ratios, generating CLKOUT/CLOUTKB frequencies ranging from 12.5 MHz to 500 MHz with a clock input reference (REFCLK) ranging from 19 MHz to 125 MHz. See...