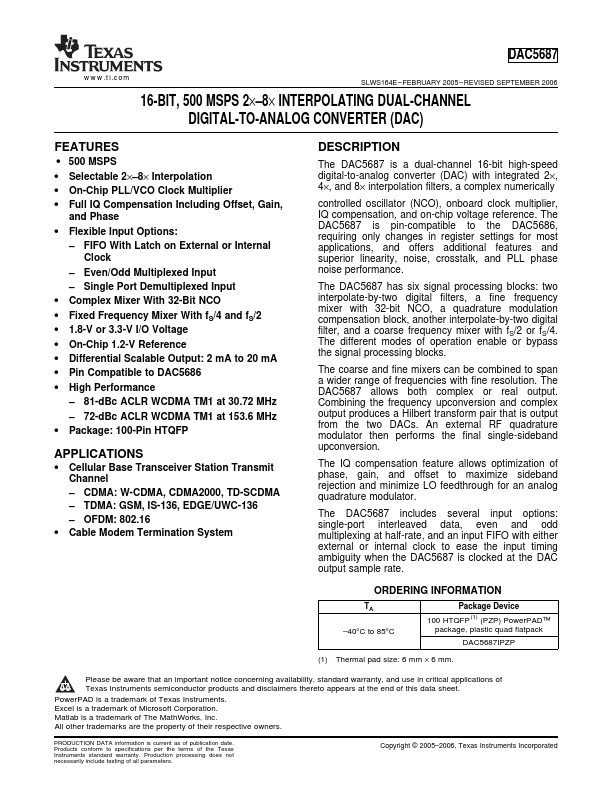

DAC5687

FEATURES

- 2345 500 MSPS

- Selectable 2×- 8× Interpolation

- On-Chip PLL/VCO Clock Multiplier

- Full IQ pensation Including Offset, Gain, and Phase

- Flexible Input Options:

- FIFO With Latch on External or Internal Clock

- Even/Odd Multiplexed Input

- Single Port Demultiplexed Input

- plex Mixer With 32-Bit NCO

- Fixed Frequency Mixer With f S/4 and f S/2

- 1.8-V or 3.3-V I/O Voltage

- On-Chip 1.2-V Reference

- Differential Scalable Output: 2 m A to 20 m A

- Pin patible to DAC5686

- High Performance

- 81-d Bc ACLR WCDMA TM1 at 30.72 MHz

- 72-d Bc ACLR WCDMA TM1 at 153.6 MHz

- Package: 100-Pin HTQFP

APPLICATIONS

- Cellular Base Transceiver Station Transmit Channel

- CDMA: W-CDMA, CDMA2000, TD-SCDMA

- TDMA: GSM, IS-136, EDGE/UWC-136

- OFDM: 802.16

- Cable Modem Termination System

DESCRIPTION

The DAC5687 is a dual-channel 16-bit high-speed digital-to-analog converter (DAC) with integrated 2×, 4×, and 8× interpolation filters, a plex numerically controlled oscillator (NCO), onboard clock...