DS90CR561

Description

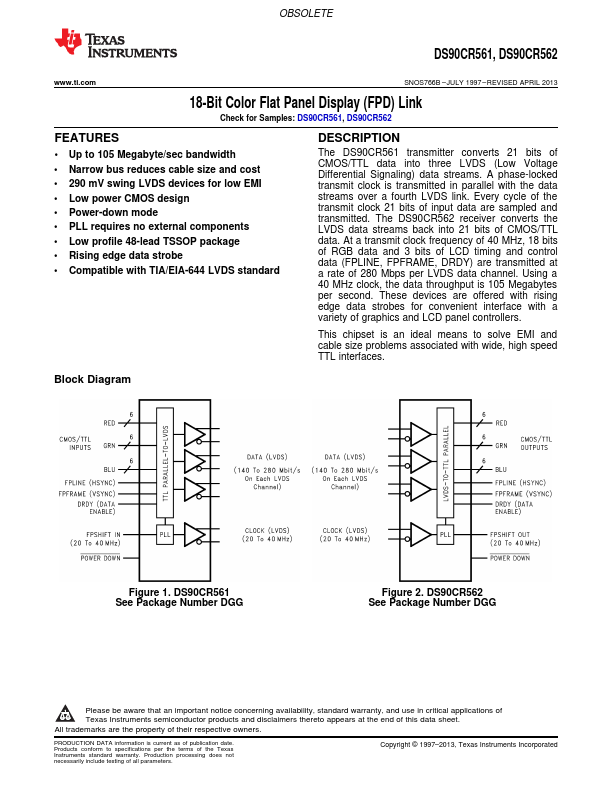

The DS90CR561 transmitter converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams.

Key Features

- 2 Up to 105 Megabyte/sec bandwidth

- Narrow bus reduces cable size and cost

- 290 mV swing LVDS devices for low EMI

- Low power CMOS design

- Power-down mode

- Low profile 48-lead TSSOP package

- Rising edge data strobe