LMK04228

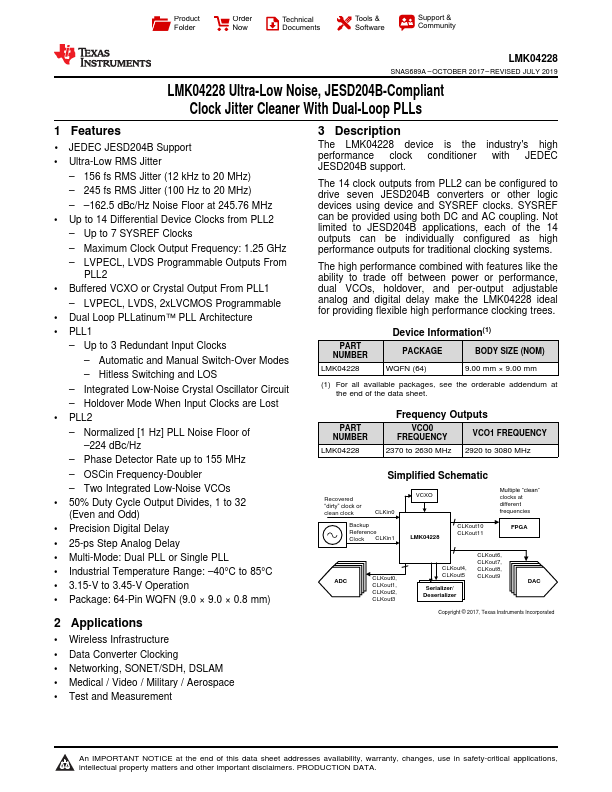

LMK04228 is Clock Jitter Cleaner manufactured by Texas Instruments.

Features

- 1 JEDEC JESD204B Support

- Ultra-Low RMS Jitter

- 156 fs RMS Jitter (12 k Hz to 20 MHz)

- 245 fs RMS Jitter (100 Hz to 20 MHz)

- - 162.5 d Bc/Hz Noise Floor at 245.76 MHz

- Up to 14 Differential Device Clocks from PLL2

- Up to 7 SYSREF Clocks

- Maximum Clock Output Frequency: 1.25 GHz

- LVPECL, LVDS Programmable Outputs From

PLL2

- Buffered VCXO or Crystal Output From PLL1

- LVPECL, LVDS, 2x LVCMOS Programmable

- Dual Loop PLLatinum™ PLL Architecture

- PLL1

- Up to 3 Redundant Input Clocks

- Automatic and Manual Switch-Over Modes

- Hitless Switching and LOS

- Integrated Low-Noise Crystal Oscillator Circuit

- Holdover Mode When Input Clocks are Lost

- PLL2

- Normalized [1 Hz] PLL Noise Floor of

- 224 d Bc/Hz

- Phase Detector Rate up to 155 MHz

- OSCin Frequency-Doubler

- Two Integrated Low-Noise VCOs

- 50% Duty Cycle Output Divides, 1 to 32 (Even and Odd)

- Precision Digital Delay

- 25-ps Step Analog Delay

- Multi-Mode: Dual PLL or Single PLL

- Industrial Temperature Range:

- 40°C to 85°C

- 3.15-V to 3.45-V Operation

- Package: 64-Pin WQFN (9.0 × 9.0 × 0.8 mm)

2 Applications

- Wireless Infrastructure

- Data Converter Clocking

- Networking, SONET/SDH, DSLAM

- Medical / Video / Military / Aerospace

- Test and...