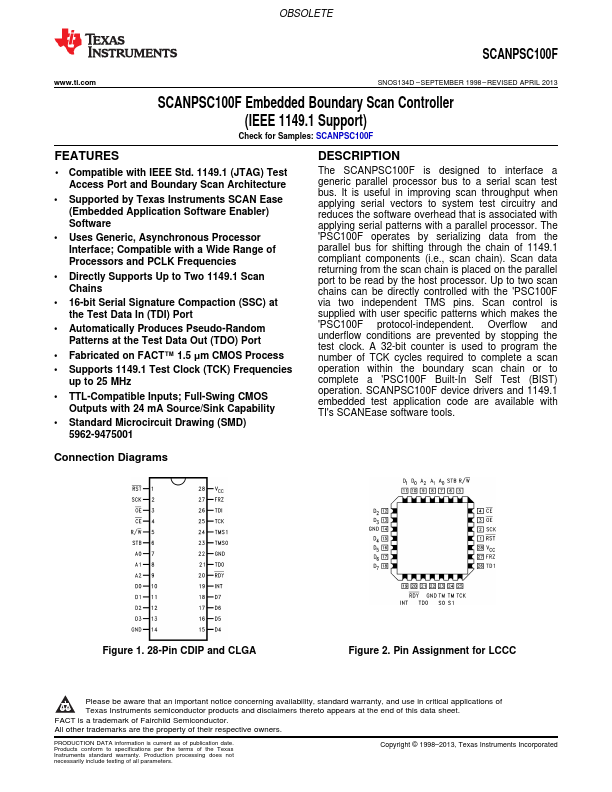

SCANPSC100F

Overview

The SCANPSC100F is designed to interface a generic parallel processor bus to a serial scan test bus. It is useful in improving scan throughput when applying serial vectors to system test circuitry and reduces the software overhead that is associated with applying serial patterns with a parallel processor.

- 23 Compatible with IEEE Std. 1149.1 (JTAG) Test Access Port and Boundary Scan Architecture

- Supported by Texas Instruments SCAN Ease (Embedded Application Software Enabler) Software

- Uses Generic, Asynchronous Processor Interface; Compatible with a Wide Range of Processors and PCLK Frequencies

- Directly Supports Up to Two 1149.1 Scan Chains

- 16-bit Serial Signature Compaction (SSC) at the Test Data In (TDI) Port

- Automatically Produces Pseudo-Random Patterns at the Test Data Out (TDO) Port

- Fabricated on FACT™ 1.5 μm CMOS Process

- Supports 1149.1 Test Clock (TCK) Frequencies up to 25 MHz

- TTL-Compatible Inputs; Full-Swing CMOS Outputs with 24 mA Source/Sink Capability

- Standard Microcircuit Drawing (SMD) 5962-9475001