SN65DSI86-Q1

Overview

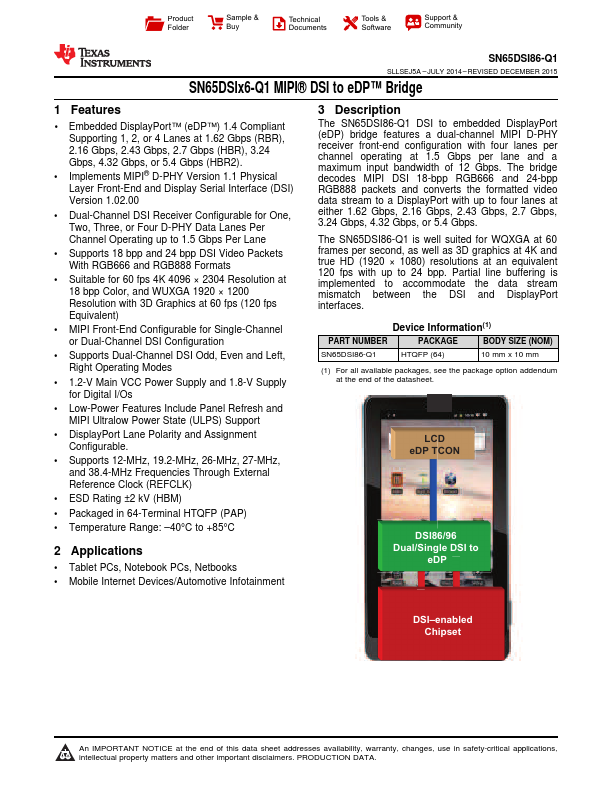

The SN65DSI86-Q1 DSI to embedded DisplayPort (eDP) bridge features a dual-channel MIPI D-PHY receiver front-end configuration with four lanes per channel operating at 1.5 Gbps per lane and a maximum input bandwidth of 12 Gbps. The bridge decodes MIPI DSI 18-bpp RGB666 and 24-bpp RGB888 packets and converts the formatted video data stream to a DisplayPort with up to four lanes at either 1.62 Gbps, 2.16 Gbps, 2.43 G.

- 1 Embedded DisplayPort™ (eDP™) 1.4 Compliant Supporting 1, 2, or 4 Lanes at 1.62 Gbps (RBR), 2.16 Gbps, 2.43 Gbps, 2.7 Gbps (HBR), 3.24 Gbps, 4.32 Gbps, or 5.4 Gbps (HBR2).

- Implements MIPI® D-PHY Version 1.1 Physical Layer Front-End and Display Serial Interface (DSI) Version 1.02.00

- Dual-Channel DSI Receiver Configurable for One, Two, Three, or Four D-PHY Data Lanes Per Channel Operating up to 1.5 Gbps Per Lane

- Supports 18 bpp and 24 bpp DSI Video Packets With RGB666 and RGB888 Formats

- Suitable for 60 fps 4K 4096 × 2304 Resolution at 18 bpp Color, and WUXGA 1920 × 1200 Resolution with 3D Graphics at 60 fps (120 fps Equivalent)

- MIPI Front-End Configurable for Single-Channel or Dual-Channel DSI Configuration

- Supports Dual-Channel DSI Odd, Even and Left, Right Operating Modes

- 1.2-V Main VCC Power Supply and 1.8-V Supply for Digital I/Os

- Low-Power Features Include Panel Refresh and MIPI Ultralow Power State (ULPS) Support

- DisplayPort Lane Polarity and Assignment Configurable.