SN65LVDS306 Overview

Description

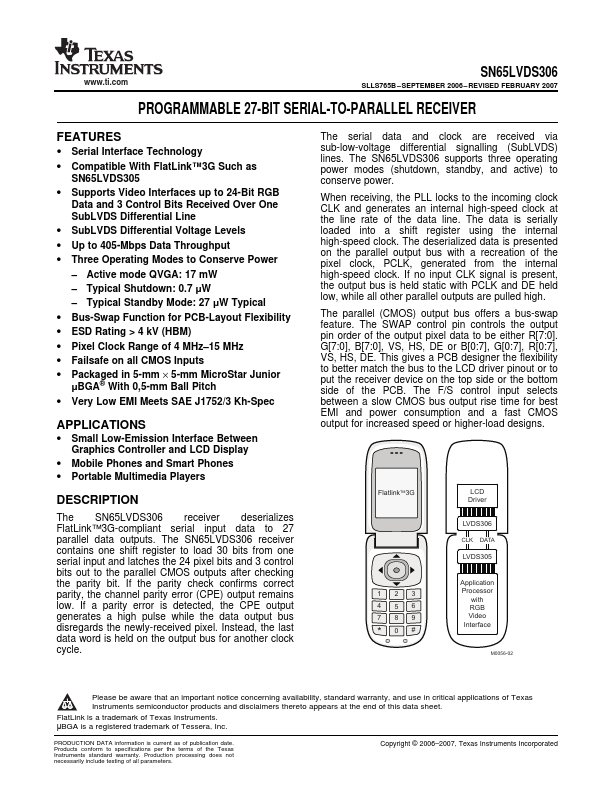

The SN65LVDS306 receiver deserializes FlatLink™3G-compliant serial input data to 27 parallel data outputs. The SN65LVDS306 receiver contains one shift register to load 30 bits from one serial input and latches the 24 pixel bits and 3 control bits out to the parallel CMOS outputs after checking the parity bit.

Key Features

- Serial Interface Technology

- Compatible With FlatLink™3G Such as SN65LVDS305

- Supports Video Interfaces up to 24-Bit RGB Data and 3 Control Bits Received Over One SubLVDS Differential Line

- SubLVDS Differential Voltage Levels

- Up to 405-Mbps Data Throughput

- Three Operating Modes to Conserve Power – Active mode QVGA: 17 mW – Typical Shutdown: 0.7 μW – Typical Standby Mode: 27 μW Typical

- Bus-Swap Function for PCB-Layout Flexibility

- ESD Rating > 4 kV (HBM)

- Pixel Clock Range of 4 MHz–15 MHz

- Failsafe on all CMOS Inputs