SN65LVDS324

FEATURES

- 23 Bridges the Interface Between Video Image Sensors and Processors

- Receives Aptina Hi SPi™, Panasonic LVDS, or Sony LVDS Parallel; Outputs 1.8V CMOS with 10/12/14/16 Bits at 18.5MHz to 162MHz

- Sub LVDS Inputs Support Up To 648Mbps

- Integrated 100Ω Differential Input Termination

- Test Image Generation Feature

- patible with TI OMAP™ and Da Vinci™

Including DM385, DM8127, DM36x, and DMVA

- Low Power 1.8V CMOS Process

- Configurable Output Conventions

- Packaged in 4.5 x 7mm BGA

APPLICATIONS

- IP Network Cameras

- Machine Vision

- Video Conferencing

- Gesture Recognition

DESCRIPTION

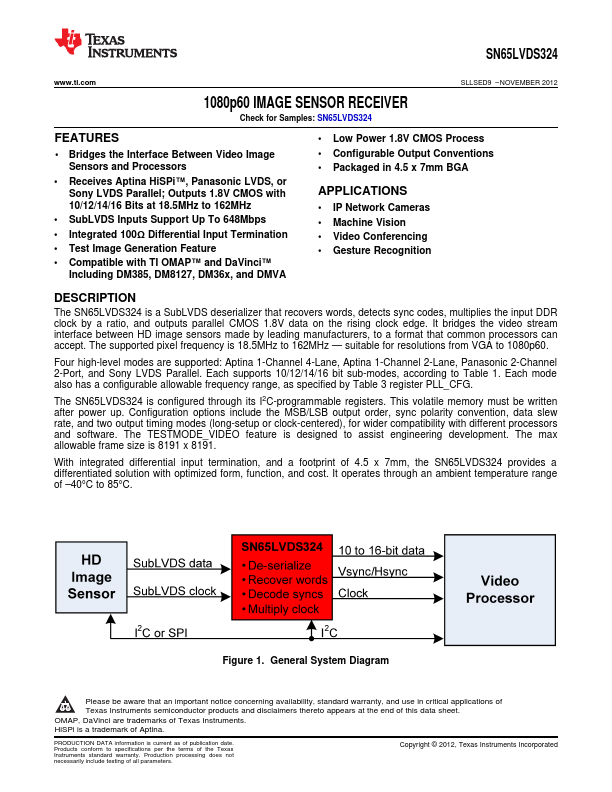

The SN65LVDS324 is a Sub LVDS deserializer that recovers words, detects sync codes, multiplies the input DDR clock by a ratio, and outputs parallel CMOS 1.8V data on the rising clock edge. It bridges the video stream interface between HD image sensors made by leading manufacturers, to a format that mon processors can accept. The supported pixel frequency is 18.5MHz to 162MHz

- suitable for...