SN65LVDS84AQ-Q1 Overview

Key Features

- 2 21:3 Data Channel Compression at up to 196 Mbytes/s Throughput

- Suited for SVGA, XGA, or SXGA Data Transmission From Controller to Display With Very Low EMI

- 21 Data Channels Plus Clock In Low-Voltage TTL Inputs and 3 Data Channels Plus Clock Out Low-Voltage Differential Signaling (LVDS) Outputs

- Operates From a Single 3.3-V Supply and 89 mW (Typ)

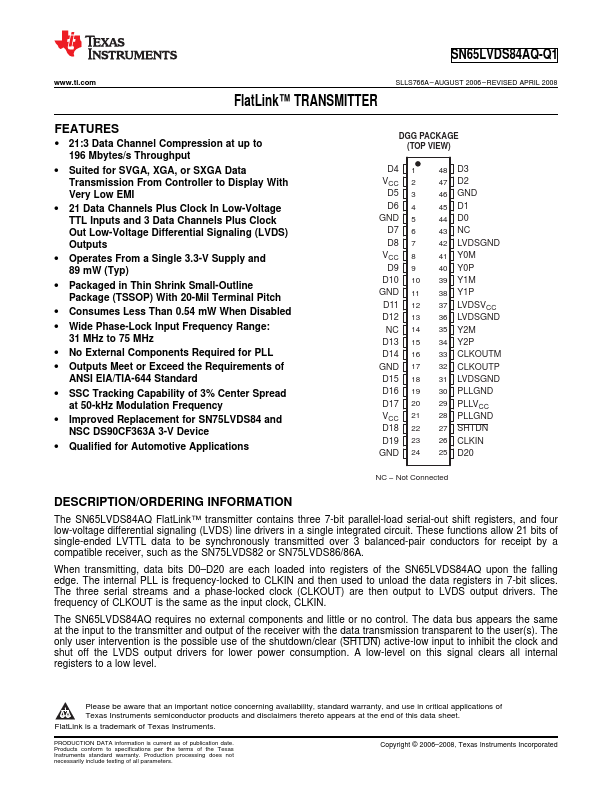

- Packaged in Thin Shrink Small-Outline Package (TSSOP) With 20-Mil Terminal Pitch