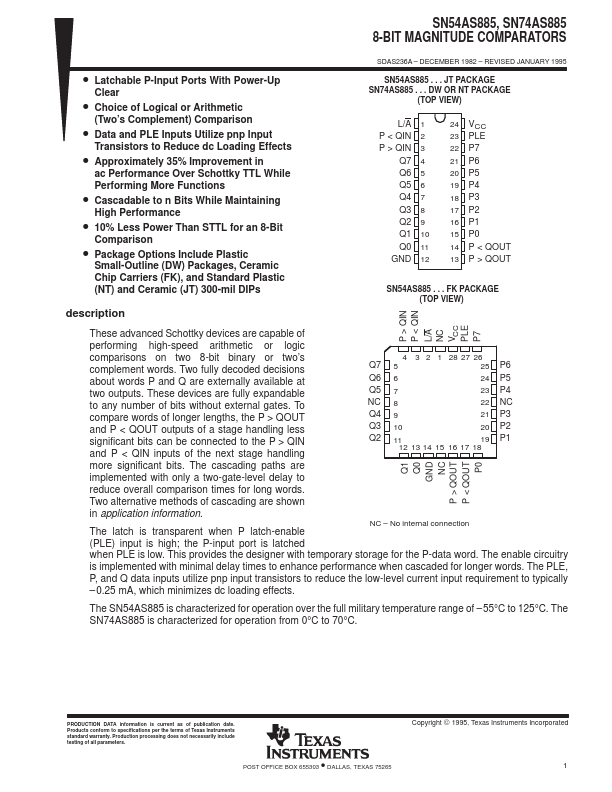

| Part | SN74AS885 |

|---|---|

| Description | 8-BIT MAGNITUDE COMPARATORS |

| Category | Comparator |

| Manufacturer | Texas Instruments |

| Size | 391.98 KB |

Pricing from 14.18 USD, available from Rochester Electronics and DigiKey.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 6497 | 25+ : 14.18 USD 100+ : 13.47 USD 500+ : 12.76 USD 1000+ : 12.05 USD |

View Offer |

| DigiKey | 3 | 1+ : 22.56 USD | View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| LM393 | STMicroelectronics | Low-power dual-voltage comparators |

| CMP401 | Analog Devices | Low Voltage Comparators |

| CMP402 | Analog Devices | Low Voltage Comparators |