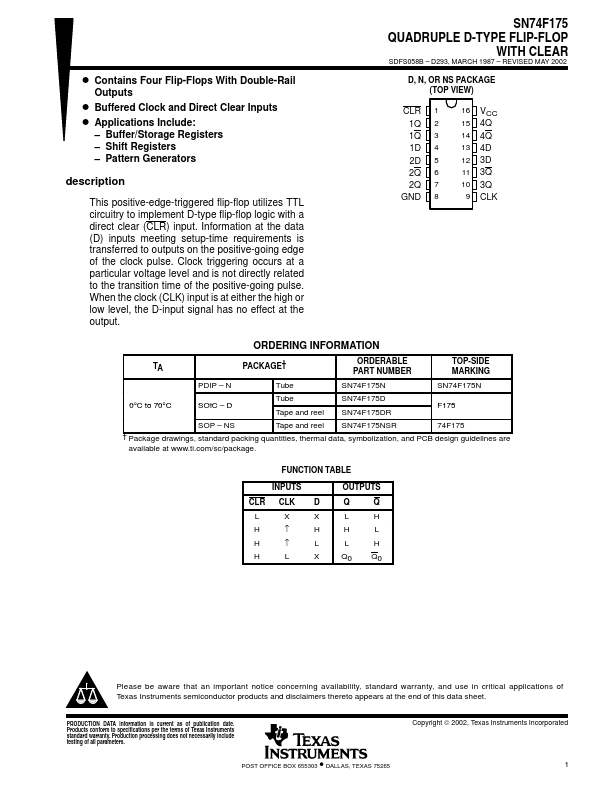

SN74F175 Overview

Key Specifications

Package: PDIP

Mount Type: Through Hole

Pins: 16

Operating Voltage: 5 V

Description

This positive-edge-triggered flip-flop utilizes TTL circuitry to implement D-type flip-flop logic with a direct clear (CLR) input. Information at the data (D) inputs meeting setup-time requirements is transferred to outputs on the positive-going edge of the clock pulse.