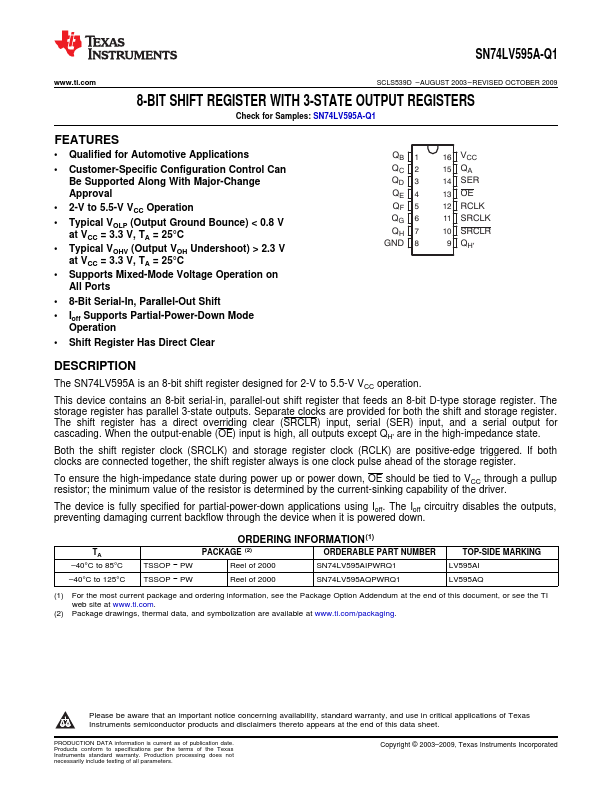

SN74LV595A-Q1 Overview

Key Specifications

Output Type (varies by manufacturer): CMOS

Description

The SN74LV595A is an 8-bit shift register designed for 2-V to 5.5-V VCC operation. This device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit D-type storage register.

Key Features

- Qualified for Automotive Applications

- Customer-Specific Configuration Control Can Be Supported Along With Major-Change Approval

- 2-V to 5.5-V VCC Operation

- Typical VOLP (Output Ground Bounce) < 0.8 V at VCC = 3.3 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot) > 2.3 V at VCC = 3.3 V, TA = 25°C