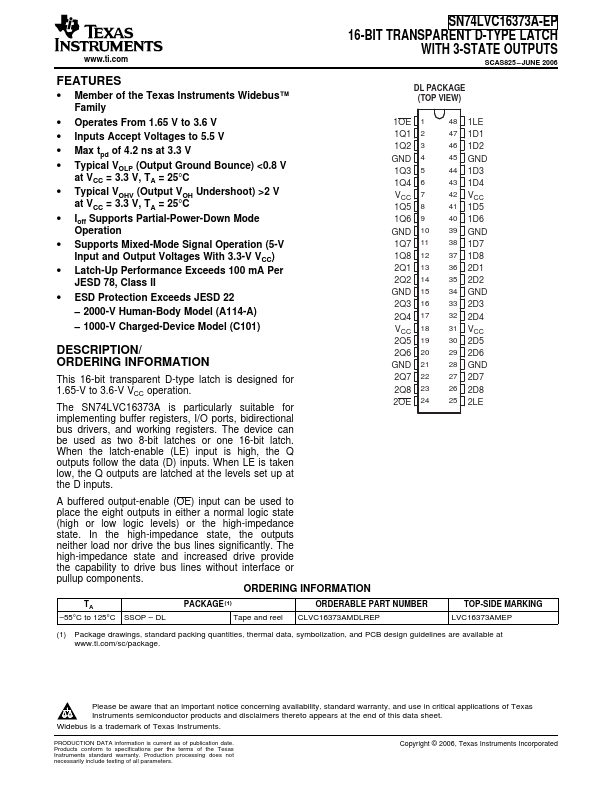

SN74LVC16373A-EP Overview

Key Specifications

Output Type (varies by manufacturer): CMOS

Key Features

- Member of the Texas Instruments Widebus™ Family

- Operates From 1.65 V to 3.6 V

- Inputs Accept Voltages to 5.5 V

- Max tpd of 4.2 ns at 3.3 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25°C