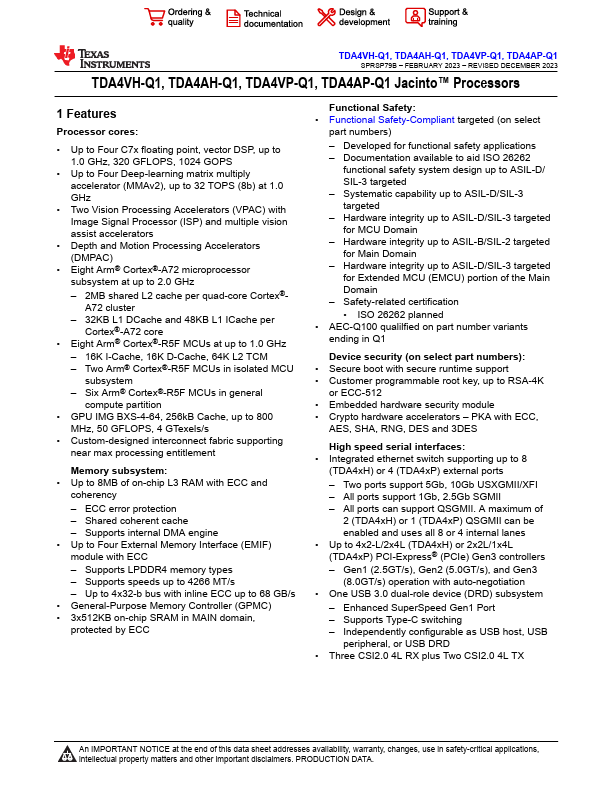

TDA4AP-Q1 Overview

Key Features

- Up to Four C7x floating point, vector DSP, up to 1.0 GHz, 320 GFLOPS, 1024 GOPS

- Up to Four Deep-learning matrix multiply accelerator (MMAv2), up to 32 TOPS (8b) at 1.0 GHz

- Two Vision Processing Accelerators (VPAC) with Image Signal Processor (ISP) and multiple vision assist accelerators

- Depth and Motion Processing Accelerators (DMPAC)

- GPU IMG BXS-4-64, 256kB Cache, up to 800 MHz, 50 GFLOPS, 4 GTexels/s

- Custom-designed interconnect fabric supporting near max processing entitlement Memory subsystem

- Up to 8MB of on-chip L3 RAM with ECC and coherency – ECC error protection – Shared coherent cache – Supports internal DMA engine

- General-Purpose Memory Controller (GPMC)

- 3x512KB on-chip SRAM in MAIN domain, protected by ECC Functional Safety