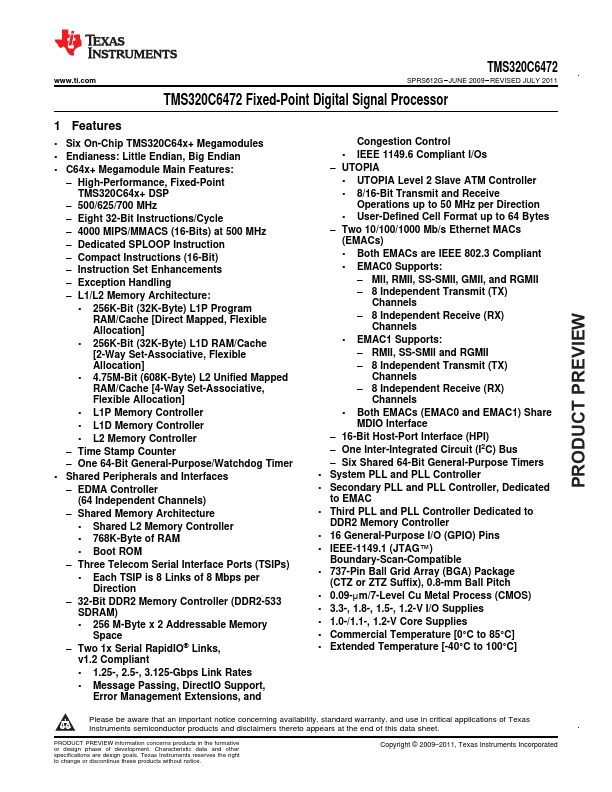

TMS320C6472

TMS320C6472 is Fixed-Point Digital Signal Processor manufactured by Texas Instruments.

Features

- Six On-Chip TMS320C64x+ Megamodules

- Endianess: Little Endian, Big Endian

- C64x+ Megamodule Main Features

:

- High-Performance, Fixed-Point TMS320C64x+ DSP

- 500/625/700 MHz

- Eight 32-Bit Instructions/Cycle

- 4000 MIPS/MMACS (16-Bits) at 500 MHz

- Dedicated SPLOOP Instruction

- pact Instructions (16-Bit)

- Instruction Set Enhancements

- Exception Handling

- L1/L2 Memory Architecture:

- 256K-Bit (32K-Byte) L1P Program RAM/Cache [Direct Mapped, Flexible Allocation]

- 256K-Bit (32K-Byte) L1D RAM/Cache [2-Way Set-Associative, Flexible Allocation]

- 4.75M-Bit (608K-Byte) L2 Unified Mapped RAM/Cache [4-Way Set-Associative, Flexible Allocation]

- L1P Memory Controller

- L1D Memory Controller

- L2 Memory Controller

- Time Stamp Counter

- One 64-Bit General-Purpose/Watchdog Timer

- Shared Peripherals and Interfaces

- EDMA Controller (64 Independent Channels)

- Shared Memory Architecture

- Shared L2 Memory Controller

- 768K-Byte of RAM

- Boot ROM

- Three Tele Serial Interface Ports (TSIPs)

- Each TSIP is 8 Links of 8 Mbps per

Direction

- 32-Bit DDR2 Memory Controller (DDR2-533

SDRAM)

- 256 M-Byte x 2 Addressable Memory

Space

- Two 1x Serial Rapid IO® Links, v1.2 pliant

- 1.25-, 2.5-, 3.125-Gbps Link Rates

- Message Passing, Direct IO Support,

Error Management Extensions,...