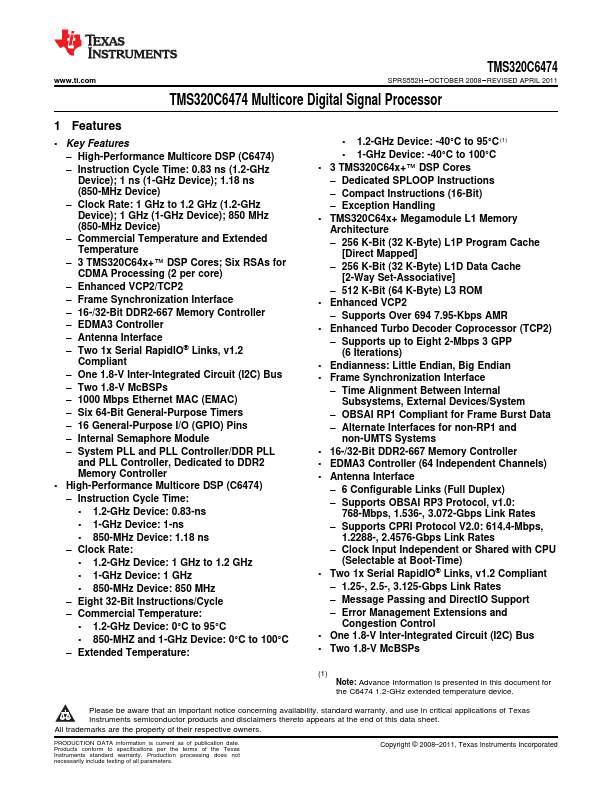

TMS320C6474

TMS320C6474 is Multicore Digital Signal Processor manufactured by Texas Instruments.

Features

- Key Features

- High-Performance Multicore DSP (C6474)

- Instruction Cycle Time: 0.83 ns (1.2-GHz Device); 1 ns (1-GHz Device); 1.18 ns (850-MHz Device)

- Clock Rate: 1 GHz to 1.2 GHz (1.2-GHz Device); 1 GHz (1-GHz Device); 850 MHz (850-MHz Device)

- mercial Temperature and Extended Temperature

- 3 TMS320C64x+™ DSP Cores; Six RSAs for CDMA Processing (2 per core)

- Enhanced VCP2/TCP2

- Frame Synchronization Interface

- 16-/32-Bit DDR2-667 Memory Controller

- EDMA3 Controller

- Antenna Interface

- Two 1x Serial Rapid IO® Links, v1.2 pliant

- One 1.8-V Inter-Integrated Circuit (I2C) Bus

- Two 1.8-V Mc BSPs

- 1000 Mbps Ethernet MAC (EMAC)

- Six 64-Bit General-Purpose Timers

- 16 General-Purpose I/O (GPIO) Pins

- Internal Semaphore Module

- System PLL and PLL Controller/DDR PLL and PLL Controller, Dedicated to DDR2 Memory Controller

- High-Performance Multicore DSP (C6474)

- Instruction Cycle Time:

- 1.2-GHz Device: 0.83-ns

- 1-GHz Device: 1-ns

- 850-MHz Device: 1.18 ns

- Clock Rate:

- 1.2-GHz Device: 1 GHz to 1.2 GHz

- 1-GHz Device: 1 GHz

- 850-MHz Device: 850 MHz

- Eight 32-Bit Instructions/Cycle

- mercial Temperature:

- 1.2-GHz Device: 0°C to 95°C

- 850-MHZ and 1-GHz Device: 0°C to 100°C

- Extended Temperature:

- 1.2-GHz Device: -40°C to 95°C(1)

- 1-GHz Device: -40°C to 100°C

- 3 TMS320C64x+™ DSP Cores

- Dedicated SPLOOP Instructions

- pact Instructions...