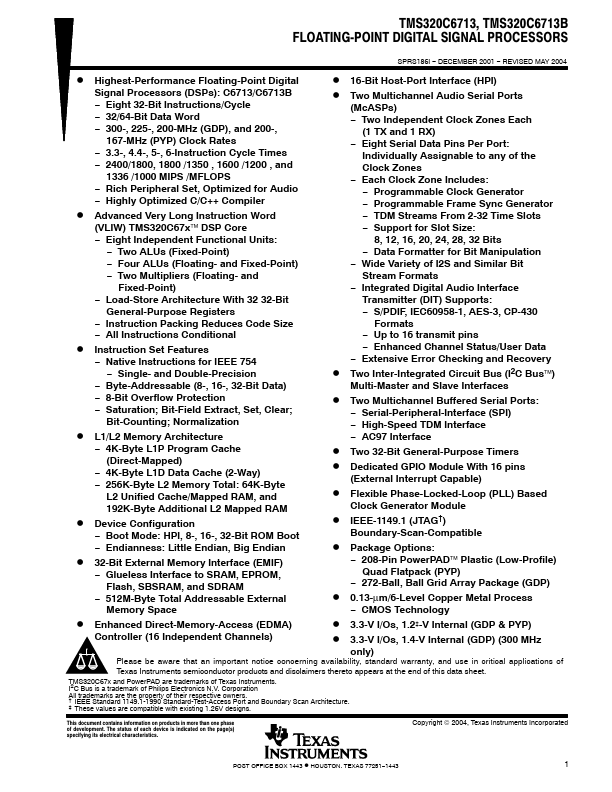

TMS320C6713

TMS320C6713 is Floating-Point Digital Signal Processor manufactured by Texas Instruments.

Features

- Native Instructions for IEEE 754

- Single- and Double-Precision

- Byte-Addressable (8-, 16-, 32-Bit Data)

- 8-Bit Overflow Protection

- Saturation; Bit-Field Extract, Set, Clear;

Bit-Counting; Normalization

D L1/L2 Memory Architecture

- 4K-Byte L1P Program Cache (Direct-Mapped)

- 4K-Byte L1D Data Cache (2-Way)

- 256K-Byte L2 Memory Total: 64K-Byte

L2 Unified Cache/Mapped RAM, and 192K-Byte Additional L2 Mapped RAM

D Device Configuration

- Boot Mode: HPI, 8-, 16-, 32-Bit ROM Boot

- Endianness: Little Endian, Big Endian

D 32-Bit External Memory Interface (EMIF)

- Glueless Interface to SRAM, EPROM, Flash, SBSRAM, and SDRAM

- 512M-Byte Total Addressable External Memory Space

D 16-Bit Host-Port Interface (HPI) D Two Multichannel Audio Serial Ports

(Mc ASPs)

- Two Independent Clock Zones Each

(1 TX and 1 RX)

- Eight Serial Data Pins Per Port:

Individually Assignable to any of the Clock Zones

- Each Clock Zone Includes:

- Programmable Clock Generator

- Programmable Frame Sync Generator

- TDM Streams From 2-32 Time Slots

- Support for Slot Size:

8, 12, 16, 20, 24, 28, 32 Bits

- Data Formatter for Bit Manipulation

- Wide Variety of I2S and Similar Bit Stream Formats

- Integrated Digital Audio Interface Transmitter (DIT) Supports:

- S/PDIF, IEC60958-1, AES-3, CP-430

Formats

- Up to 16 transmit pins

- Enhanced Channel Status/User Data

- Extensive Error Checking and Recovery

D Two Inter-Integrated Circuit Bus (I2C Bus)

Multi-Master and Slave...