TPIC1321L Description

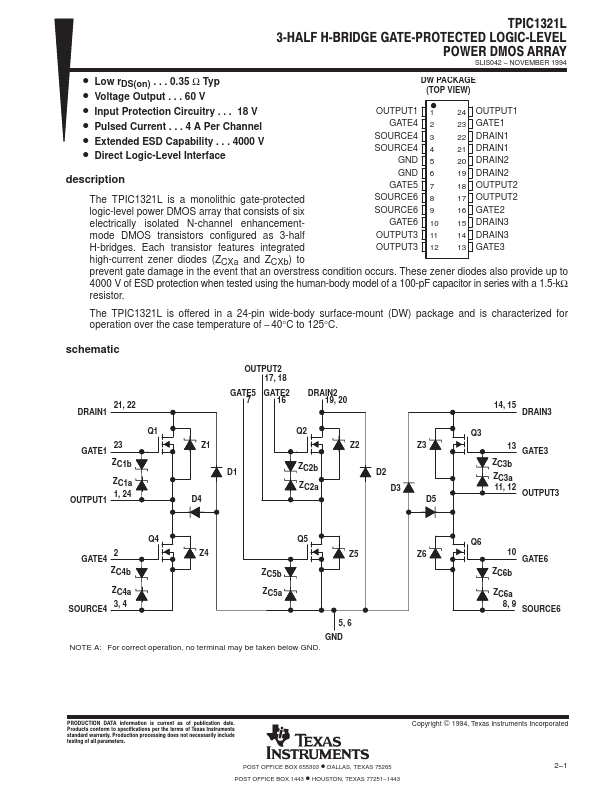

GND 6 GATE5 7 19 DRAIN2 18 OUTPUT2 The TPIC1321L is a monolithic gate-protected SOURCE6 8 17 OUTPUT2 logic-level power DMOS array that consists of six SOURCE6 9 16 GATE2 electrically isolated N-channel enhancement- GATE6 10 15 DRAIN3 mode DMOS transistors.

TPIC1321L Key Features

- 40°C to 125°C

- POST OFFICE BOX 655303 DALLAS, TEXAS 75265

- POST OFFICE BOX 1443 HOUSTON, TEXAS 77251-1443

- NOVEMBER 1994