TPIC5421L

TPIC5421L is logic-level power DMOS array manufactured by Texas Instruments.

description

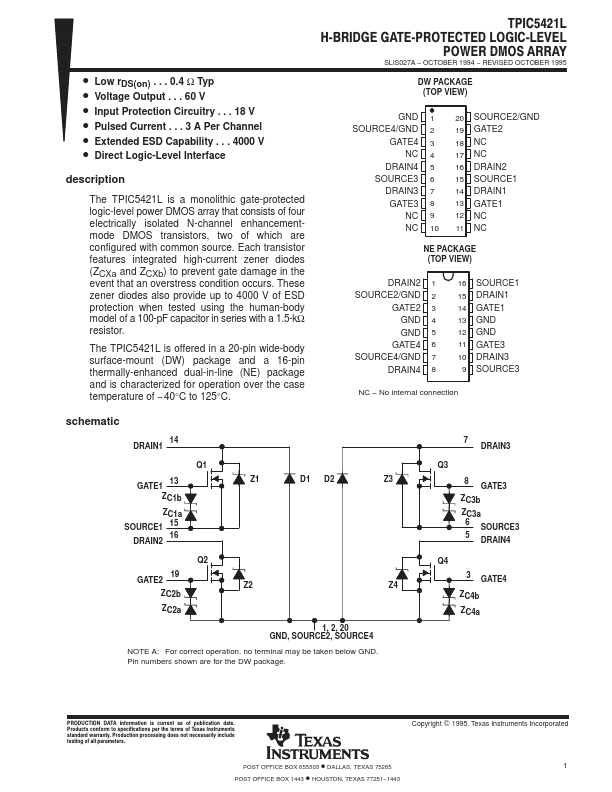

The TPIC5421L is a monolithic gate-protected logic-level power DMOS array that consists of four electrically isolated N-channel enhancementmode DMOS transistors, two of which are configured with mon source. Each transistor features integrated high-current zener diodes (ZCXa and ZCXb) to prevent gate damage in the event that an overstress condition occurs. These zener diodes also provide up to 4000 V of ESD protection when tested using the human-body model of a 100-p F capacitor in series with a 1.5-kΩ resistor.

The TPIC5421L is offered in a 20-pin wide-body surface-mount (DW) package and a 16-pin thermally-enhanced dual-in-line (NE) package and is characterized for operation over the case temperature of

- 40°C to 125°C.

TPIC5421L HĆBRIDGE GATEĆPROTECTED LOGICĆLEVEL

POWER DMOS ARRAY

SLIS027A

- OCTOBER 1994

- REVISED OCTOBER 1995

DW PACKAGE (TOP VIEW)

GND SOURCE4/GND

GATE4 NC

DRAIN4 SOURCE3

DRAIN3 GATE3

NC NC

1 2 3 4 5 6 7 8 9 10

20 SOURCE2/GND 19 GATE2 18 NC 17 NC 16 DRAIN2 15 SOURCE1 14 DRAIN1 13 GATE1 12 NC 11 NC

NE PACKAGE (TOP VIEW)

DRAIN2 SOURCE2/GND

GATE2 GND GND

GATE4 SOURCE4/GND

DRAIN4

1 2 3 4 5 6 7 8

16 SOURCE1 15 DRAIN1 14 GATE1 13 GND 12 GND 11 GATE3 10 DRAIN3 9 SOURCE3

- No internal connection schematic

14 DRAIN1

GATE1 13 ZC1b

ZC1a SOURCE1 15

DRAIN2 16

Q1

Z1 D1 D2

Z3

19 GATE2

ZC2b ZC2a

Q2

Z2

Z4

1, 2, 20 GND, SOURCE2, SOURCE4

NOTE A: For correct operation, no terminal may be taken below GND. Pin numbers shown are for the DW...