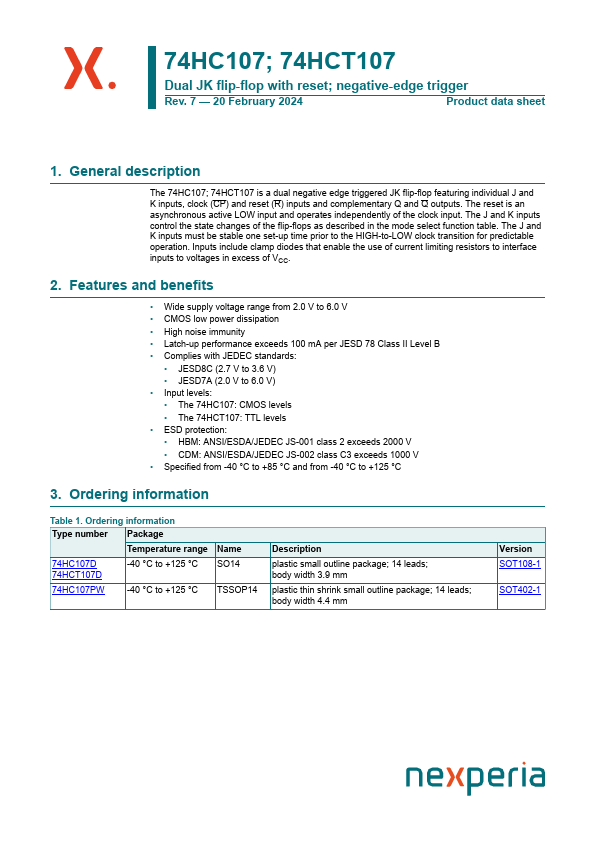

74HC107D

Description

The 74HC107; 74HCT107 is a dual negative edge triggered JK flip-flop featuring individual J and K inputs, clock (CP) and reset (R) inputs and plementary Q and Q outputs.

Key Features

- Wide supply voltage range from 2.0 V to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

- plies with JEDEC standards

- Input levels

- The 74HC107: CMOS levels

- The 74HCT107: TTL levels

- ESD protection

- HBM: ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2000 V