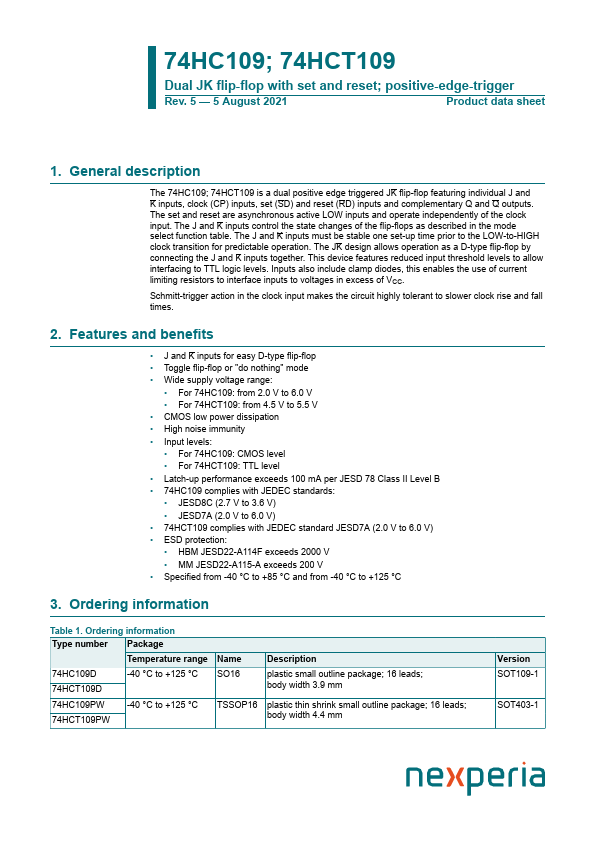

74HC109 Overview

Key Specifications

Package: SOP

Pins: 16

Operating Voltage: 4.5 V

Max Voltage (typical range): 6 V

Description

The 74HC109; 74HCT109 is a dual positive edge triggered JK flip-flop featuring individual J and K inputs, clock (CP) inputs, set (SD) and reset (RD) inputs and complementary Q and Q outputs. The set and reset are asynchronous active LOW inputs and operate independently of the clock input.

Key Features

- J and K inputs for easy D-type flip-flop

- Toggle flip-flop or "do nothing" mode

- Wide supply voltage range

- For 74HC109: from 2.0 V to 6.0 V

- For 74HCT109: from 4.5 V to 5.5 V

- CMOS low power dissipation

- High noise immunity

- Input levels

- For 74HC109: CMOS level

- For 74HCT109: TTL level