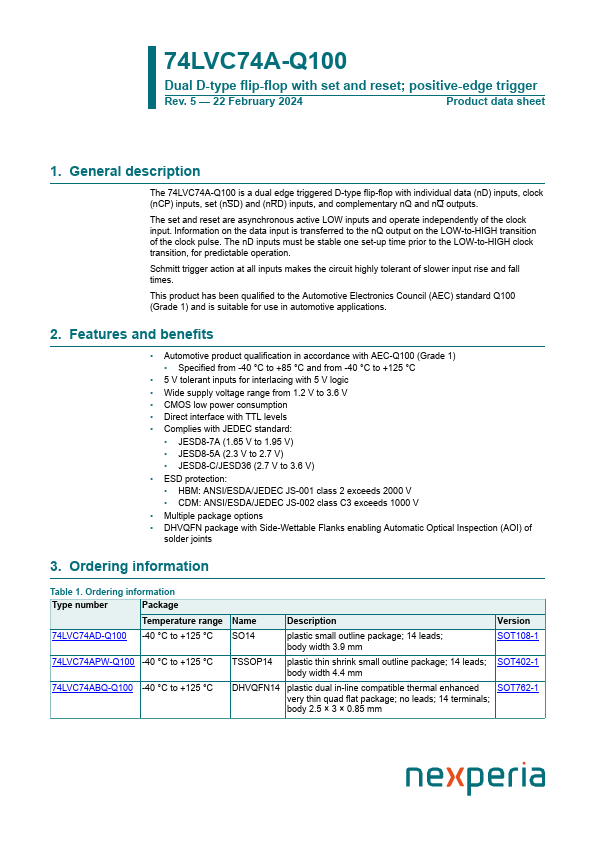

74LVC74A-Q100

74LVC74A-Q100 is Dual D-type flip-flop manufactured by Nexperia.

Dual D-type flip-flop with set and reset; positive-edge trigger

Rev. 5

- 22 February 2024

Product data sheet

1. General description

The 74LVC74A-Q100 is a dual edge triggered D-type flip-flop with individual data (nD) inputs, clock (nCP) inputs, set (nSD) and (nRD) inputs, and plementary nQ and nQ outputs.

The set and reset are asynchronous active LOW inputs and operate independently of the clock input. Information on the data input is transferred to the nQ output on the LOW-to-HIGH transition of the clock pulse. The nD inputs must be stable one set-up time prior to the LOW-to-HIGH clock transition, for predictable operation.

Schmitt trigger action at all inputs makes...