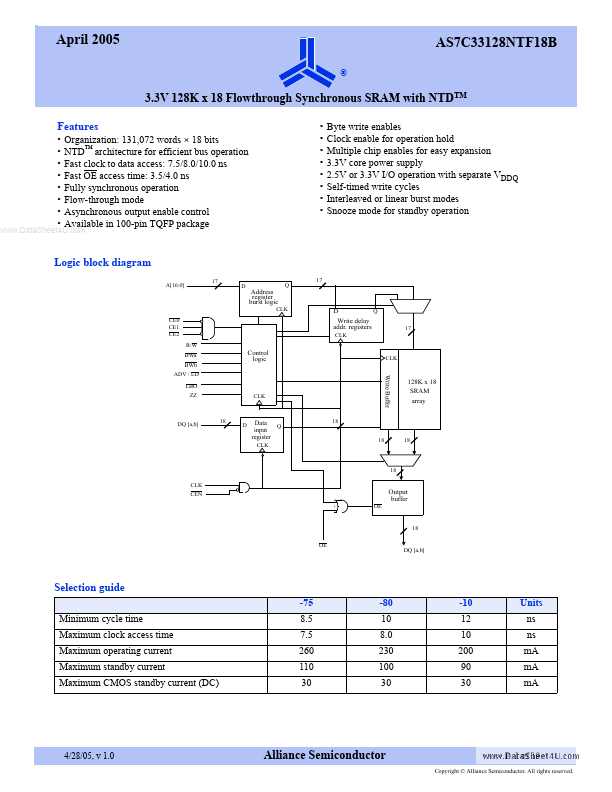

AS7C33128NTF18B Key Features

- Byte write enables Clock enable for operation hold Multiple chip enables for easy expansion 3.3V core power supply 2.5V

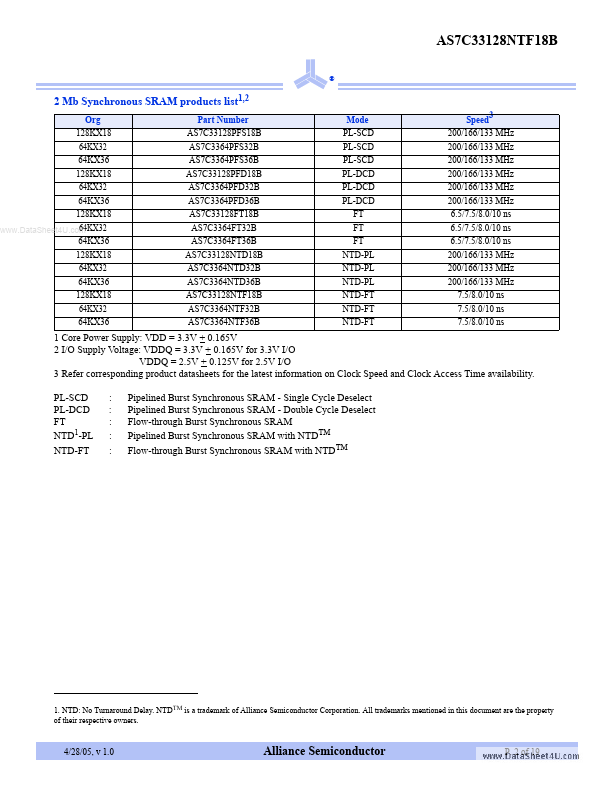

- Single Cycle Deselect Pipelined Burst Synchronous SRAM

- Double Cycle Deselect Flow-through Burst Synchronous SRAM Pipelined Burst Synchronous SRAM with NTDTM Flow-through Burst

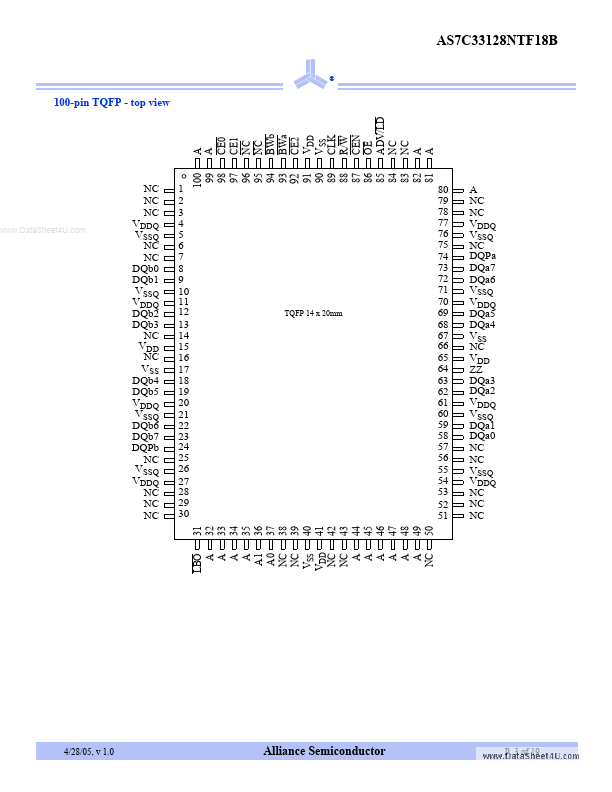

- top view