PA7572

Description

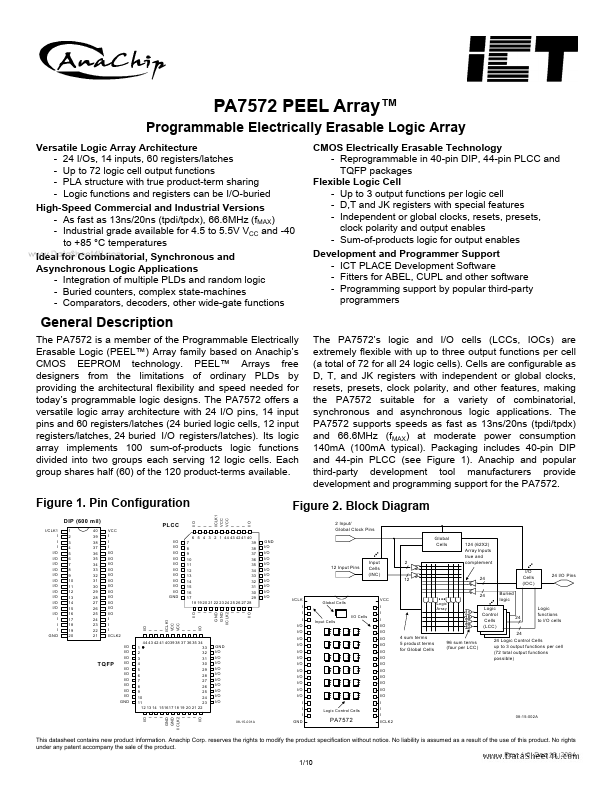

The PA7572 is a member of the Programmable Electrically Erasable Logic (PEEL™) Array family based on Anachip’s CMOS EEPROM technology. PEEL™ Arrays free designers from the limitations of ordinary PLDs by providing the architectural flexibility and speed needed for today’s programmable logic designs.