ADP7112 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 6

Max Voltage (typical range): 20 V

Min Voltage (typical range): 3.5 V

Description

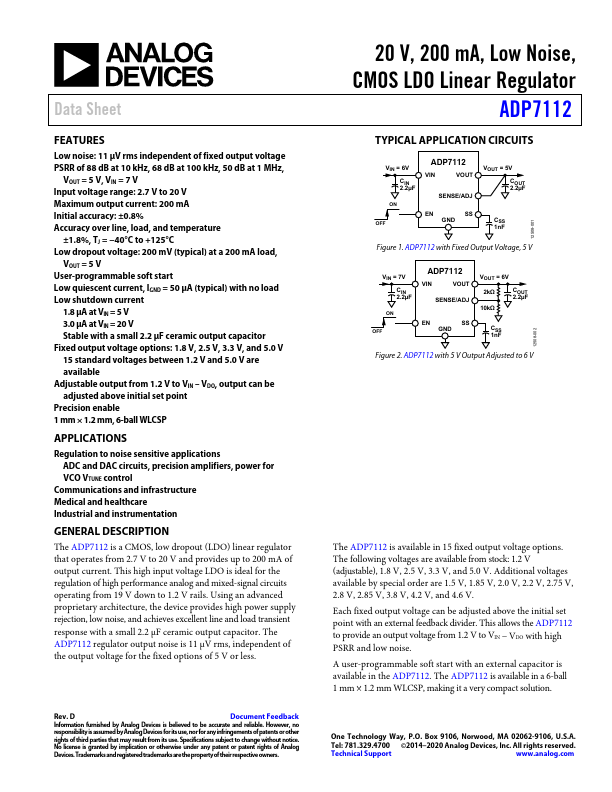

The ADP7112 is a CMOS, low dropout (LDO) linear regulator that operates from 2.7 V to 20 V and provides up to 200 mA of output current. This high input voltage LDO is ideal for the regulation of high performance analog and mixed-signal circuits operating from 19 V down to 1.2 V rails.