ADSP-2100A

ADSP-2100A is DSP Microcomputers manufactured by Analog Devices.

- Part of the ADSP-2101 comparator family.

- Part of the ADSP-2101 comparator family.

a

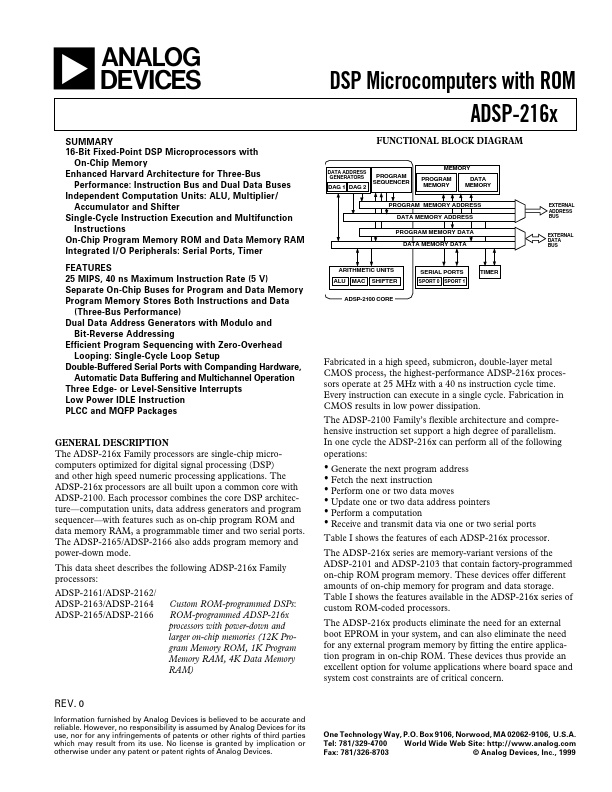

DSP Microputers with ROM

ADSP-216x

SUMMARY 16-Bit Fixed-Point DSP Microprocessors with

On-Chip Memory Enhanced Harvard Architecture for Three-Bus

Performance: Instruction Bus and Dual Data Buses Independent putation Units: ALU, Multiplier/

Accumulator and Shifter Single-Cycle Instruction Execution and Multifunction

Instructions On-Chip Program Memory ROM and Data Memory RAM Integrated I/O Peripherals: Serial Ports, Timer

Features

25 MIPS, 40 ns Maximum Instruction Rate (5 V) Separate On-Chip Buses for Program and Data Memory Program Memory Stores Both Instructions and Data

(Three-Bus Performance) Dual Data Address Generators with Modulo and

Bit-Reverse Addressing Efficient...