ADSP-SC594

ADSP-SC594 is SHARC+ Dual-Core DSP manufactured by Analog Devices.

- Part of the ADSP-21593 comparator family.

- Part of the ADSP-21593 comparator family.

SHARC+ Dual-Core DSP with Arm Cortex-A5

ADSP-21593/21594/ADSP-SC592/SC594

SYSTEM Features

Dual-enhanced SHARC+ floating-point cores High performance SHARC+ cores (up to 1 GHz each) Up to 5 Mb (640 k B) L1 SRAM memory per core with parity (optional ability to configure as cache) 32-bit, 40-bit, and 64-bit floating-point support 32-bit fixed-point support Byte, short word, word, and long word addressability

Arm Cortex-A5 core Up to 1 GHz/1600 DMIPS with NEON/VFPv4-D16 32 k B L1 instruction and data caches with parity 256 k B L2 cache with parity

Powerful DMA system with 8 Mem DMAs On-chip memory protection Integrated safety Features

17 mm × 17 mm, 400-ball BGA_ED (0.8 mm pitch),

Ro HS pliant

MEMORY

Large on-chip Level 2 (L2) SRAM with ECC protection, up to 2 MB

One Level 3 (L3) interface providing 16-bit interface to DDR3/ DDR3L SDRAM devices

ADDITIONAL Features

ADSP-2156x pin-patible package options Enhanced FIR and IIR accelerators running up to 1 GHz Security and protection

Cryptographic hardware accelerators Fast secure boot with IP protection Support for Arm Trust Zone AEC-Q100 qualified for automotive applications

APPLICATIONS

Automotive: audio amplifier, head unit, ANC/RNC, rear seat entertainment, digital cockpit, ADAS

Consumer: AVRs, mixing consoles, microphone arrays, conferencing systems

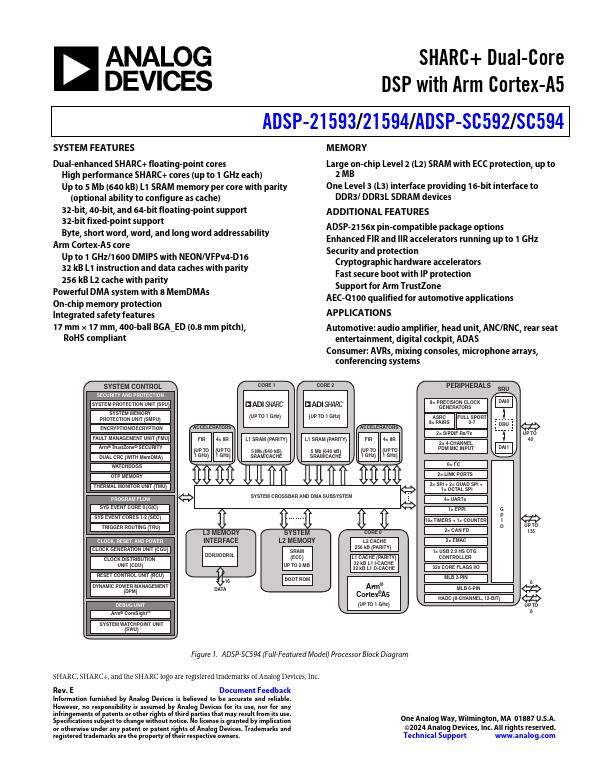

SYSTEM CONTROL

SECURITY AND PROTECTION SYSTEM PROTECTION UNIT (SPU)

SYSTEM MEMORY PROTECTION UNIT (SMPU) ENCRYPTION/DECRYPTION FAULT MANAGEMENT UNIT (FMU) Arm® Trust Zone® SECURITY DUAL CRC (WITH Mem DMA)

WATCHDOGS OTP MEMORY THERMAL MONITOR UNIT (TMU)

PROGRAM FLOW SYS EVENT CORE 0 (GIC) SYS EVENT CORES 1-2 (SEC) TRIGGER ROUTING (TRU)

CLOCK, RESET, AND POWER CLOCK GENERATION UNIT (CGU)

CLOCK DISTRIBUTION UNIT (CDU)

RESET CONTROL UNIT (RCU)

DYNAMIC POWER MANAGEMENT (DPM)

DEBUG UNIT Arm® Core Sight TM SYSTEM WATCHPOINT UNIT

(SWU)

CORE...