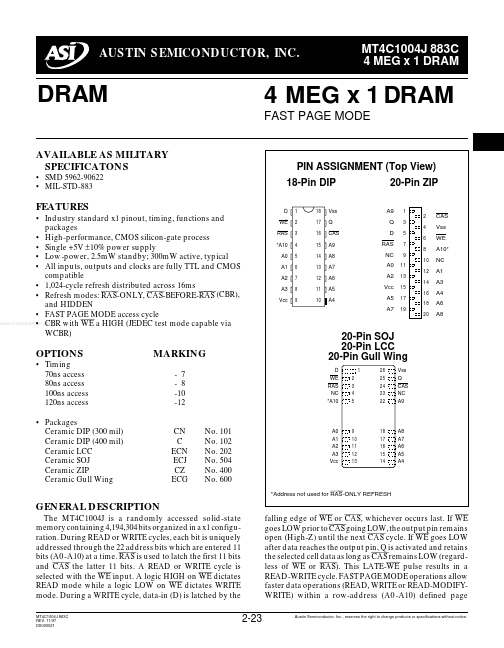

MT4C1004J883C Key Features

- Industry standard x1 pinout, timing, functions and packages

- High-performance, CMOS silicon-gate process

- Single +5V ± 10% power supply

- Low-power, 2.5mW standby; 300mW active, typical

- All inputs, outputs and clocks are fully TTL and CMOS patible

- 1,024-cycle refresh distributed across 16ms

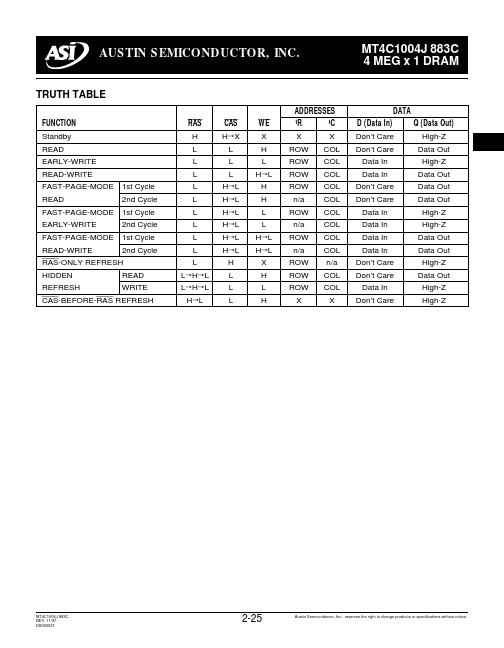

- Refresh modes: /R?A/S-ONLY, /C/A/S-BEFORE-/R/?A/S (CBR), and HIDDEN

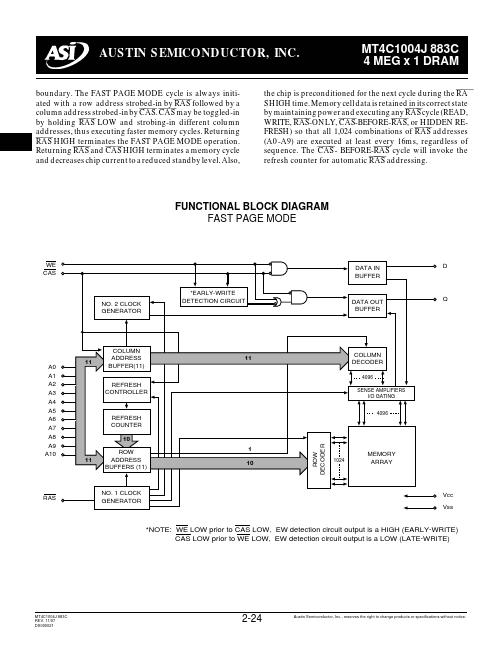

- FAST PAGE MODE access cycle

- CBR with ?W/E a HIGH (JEDEC test mode capable via WCBR)

- Timing 70ns access 80ns access 100ns access 120ns access