PXA272 Overview

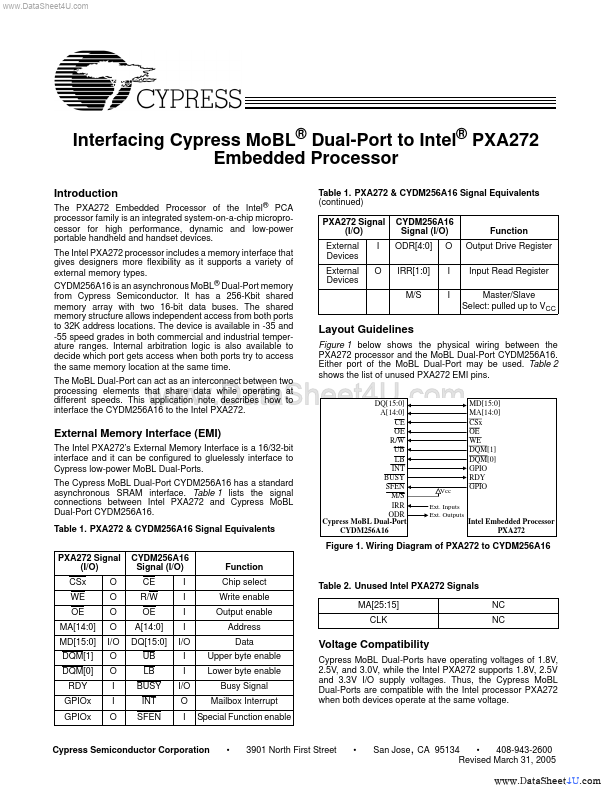

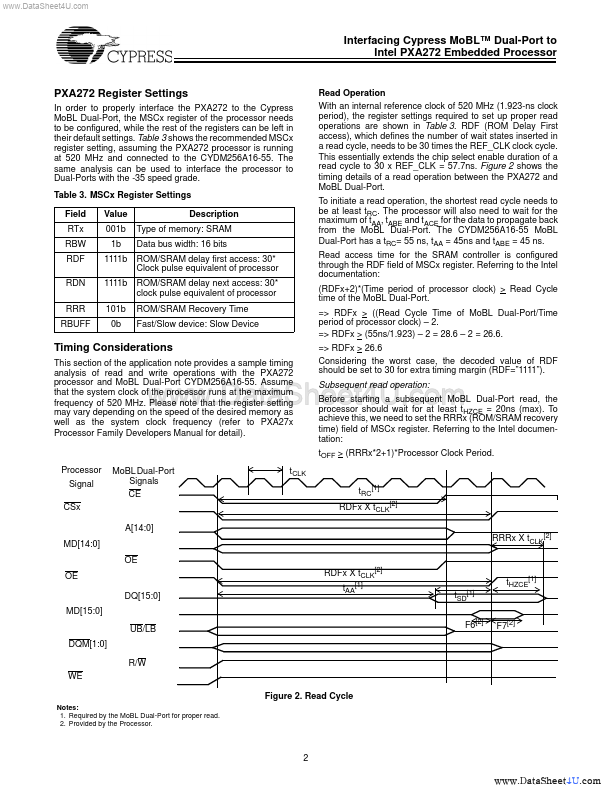

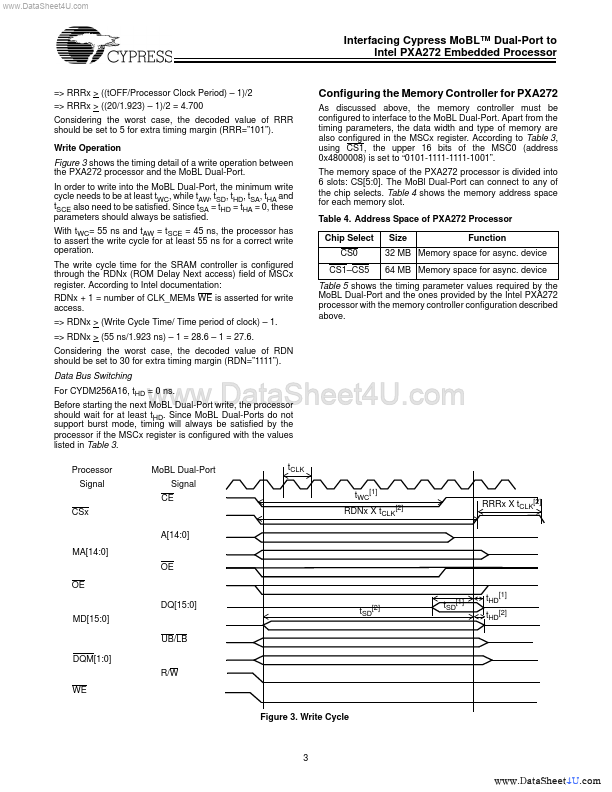

Interfacing Cypress MoBL® Dual-Port to Intel® PXA272 Embedded Processor Introduction The PXA272 Embedded Processor of the Intel® PCA processor family is an integrated system-on-a-chip microprocessor for high performance, dynamic and low-power portable handheld and handset devices. The Intel PXA272 processor includes a memory interface that gives designers more flexibility as it supports a variety of external memory...