Datasheet Summary

PRELIMINARY DATA SHEET

128M bits SDRAM

EDS1232AABB, EDS1232AATA (4M words × 32 bits)

Description

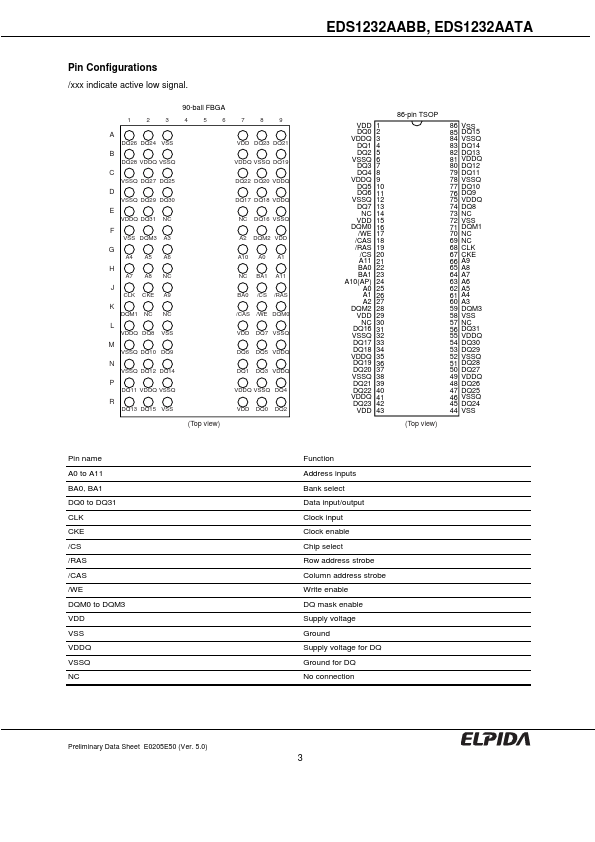

The EDS1232AA is a 128M bits SDRAM organized as 1,048,576 words × 32 bits × 4 banks. All inputs and outputs are synchronized with the positive edge of the clock. They are packaged in 90-ball FBGA, 86-pin plastic TSOP (II).

Features

- -

- -

- 3.3V power supply Clock frequency: 166MHz (max.) Single pulsed /RAS ×32 organization 4 banks can operate simultaneously and independently

- Burst read/write operation and burst read/single write operation capability

- Programmable burst length (BL): 1, 2, 4, 8 and full page

- 2 variations of burst sequence Sequential (BL = 1, 2, 4, 8) Interleave (BL =...