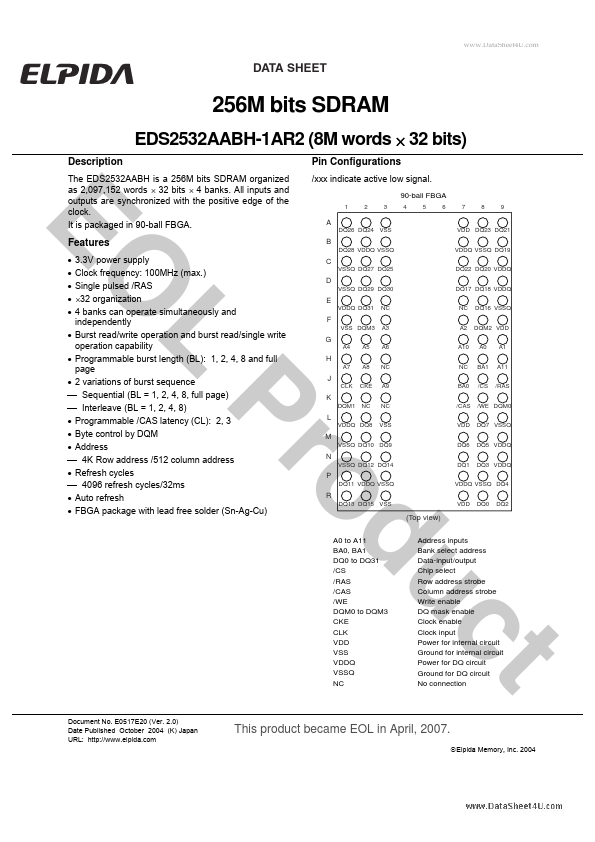

EDS2532AABH-1AR2 Description

The EDS2532AABH is a 256M bits SDRAM organized as 2,097,152 words × 32 bits × 4 banks. All inputs and outputs are synchronized with the positive edge of the clock. It is packaged in 90-ball FBGA.

EDS2532AABH-1AR2 Key Features

- Burst read/write operation and burst read/single write operation capability

- Programmable burst length (BL): 1, 2, 4, 8 and full page

- Programmable /CAS latency (CL): 2, 3

- Byte control by DQM

- Address ⎯ 4K Row address /512 column address

- Refresh cycles ⎯ 4096 refresh cycles/32ms

- Auto refresh

- FBGA package with lead free solder (Sn-Ag-Cu)

- 1 Features