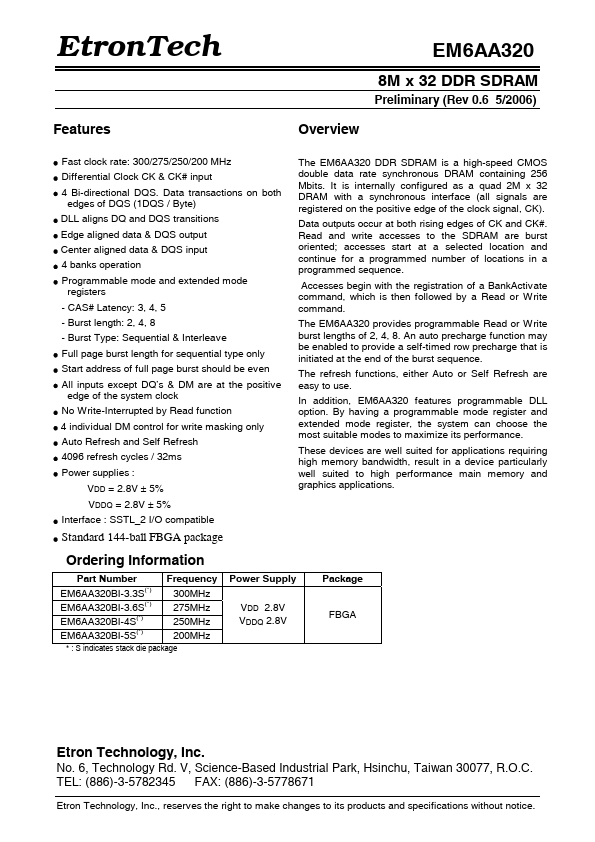

EM6AA320 Key Features

- Fast clock rate: 300/275/250/200 MHz

- Differential Clock CK & CK# input

- 4 Bi-directional DQS. Data transactions on both edges of DQS (1DQS / Byte)

- DLL aligns DQ and DQS transitions

- Edge aligned data & DQS output

- Center aligned data & DQS input

- 4 banks operation

- Programmable mode and extended mode registers

- CAS# Latency: 3, 4, 5

- Burst length: 2, 4, 8