EP520

Overview

The EP520 SDRAM controller interfaces between a processor or DMA device with an SDRAM. It performs SDRAM read and write access based on process.

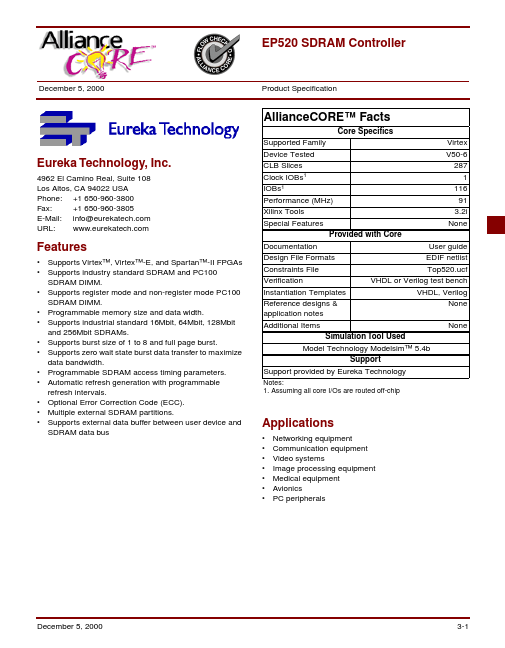

- Assuming all core I/Os are routed off-chip Eureka Technology, Inc. 4962 El Camino Real, Suite 108 Los Altos, CA 94022 USA Phone: +1 650-960-3800 Fax: +1 650-960-3805 E-Mail: info@ URL: Features * * * * * * * * * * *

- Supports Virtex™, Virtex™-E, and Spartan™-II FPGAs Supports industry standard SDRAM and PC100 SDRAM DIMM. Supports register mode and non-register mode PC100 SDRAM DIMM. Programmable memory size and data width. Supports industrial standard 16Mbit, 64Mbit, 128Mbit and 256Mbit SDRAMs. Supports burst size of 1 to 8 and full page burst. Supports zero wait state burst data transfer to maximize data bandwidth. Programmable SDRAM access timing parameters. Automatic refresh generation with programmable refresh intervals. Optional Error Correction Code (ECC). Multiple external SDRAM partitions. Supports external data buffer between user device and SDRAM data bus