XRT73L04A

XRT73L04A is 4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT manufactured by Exar.

..

4 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT

REV. 2.0.3

OCTOBER 2003

GENERAL DESCRIPTION

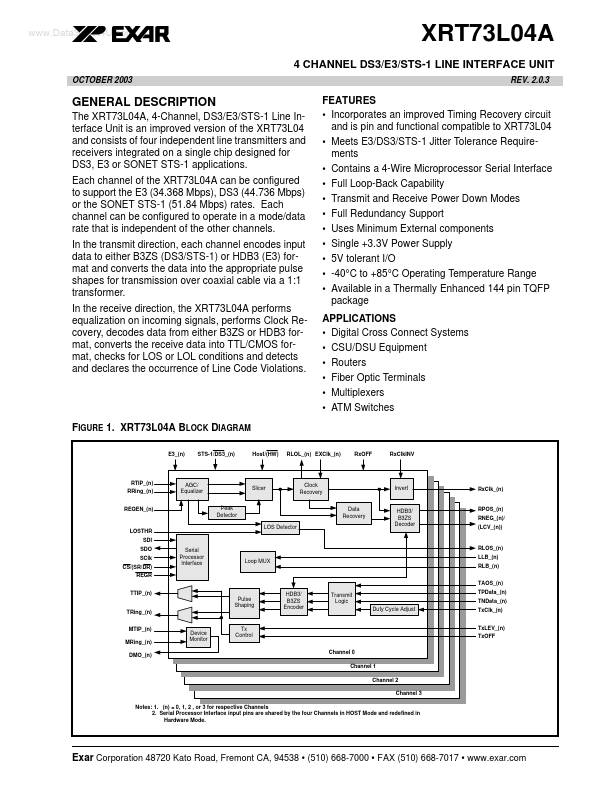

The XRT73L04A, 4-Channel, DS3/E3/STS-1 Line Interface Unit is an improved version of the XRT73L04 and consists of four independent line transmitters and receivers integrated on a single chip designed for DS3, E3 or SONET STS-1 applications. Each channel of the XRT73L04A can be configured to support the E3 (34.368 Mbps), DS3 (44.736 Mbps) or the SONET STS-1 (51.84 Mbps) rates. Each channel can be configured to operate in a mode/data rate that is independent of the other channels. In the transmit direction, each channel encodes input data to either B3ZS (DS3/STS-1) or HDB3...