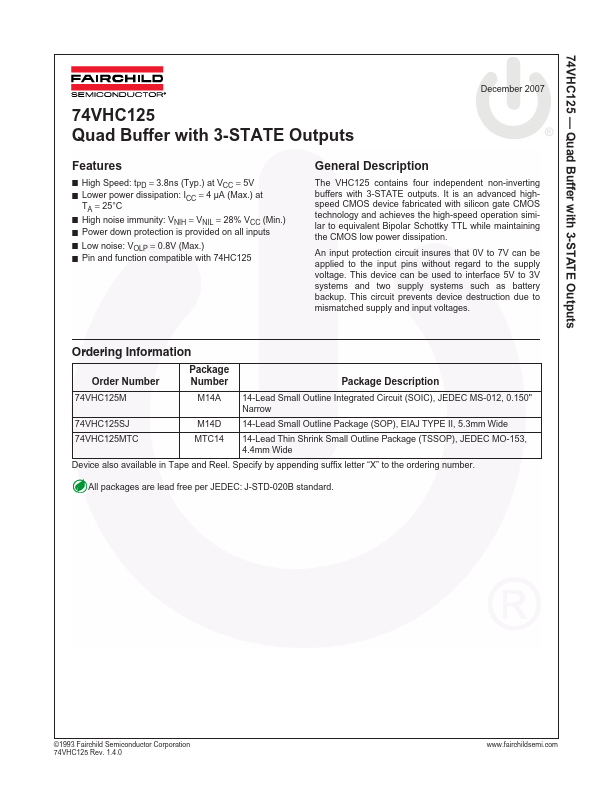

74VHC125 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 3.3 V

Description

The VHC125 contains four independent non-inverting buffers with 3-STATE outputs. It is an advanced highspeed CMOS device fabricated with silicon gate CMOS technology and achieves the high-speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

Key Features

- High Speed: tPD = 3.8ns (Typ.) at VCC = 5V

- Lower power dissipation: ICC = 4 µA (Max.) at TA = 25°C

- High noise immunity: VNIH = VNIL = 28% VCC (Min.)

- Power down protection is provided on all inputs

- Low noise: VOLP = 0.8V (Max.)