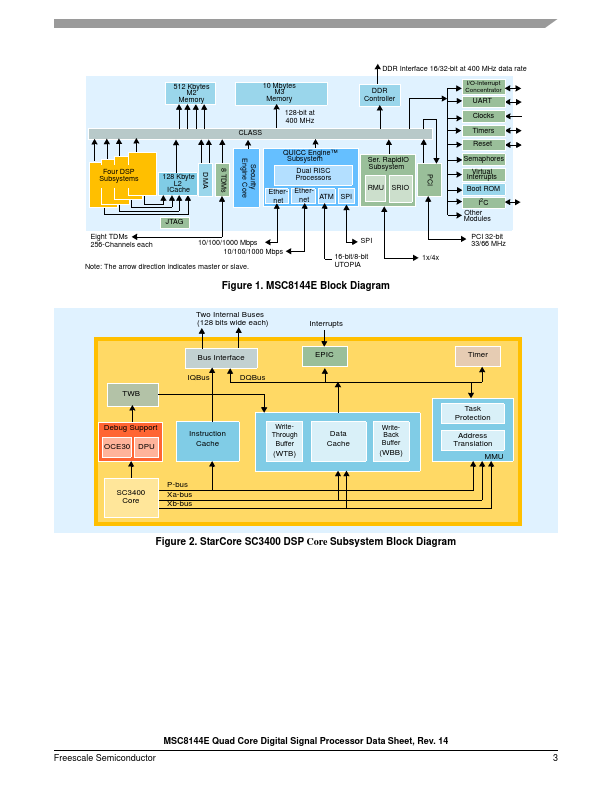

MSC8144E Overview

Freescale Semiconductor Data Sheet: Chip-level arbitration and system (CLASS) that provides full fabric non-blocking arbitration between the processing elements and other initiators and the M2 memory, DDR SRAM controller, device configuration control and status registers, and other targets. 128 Kbyte L2 shared instruction cache.