Part number:

HYMP512Uxxx

Manufacturer:

Hynix

File Size:

442.92 KB

Description:

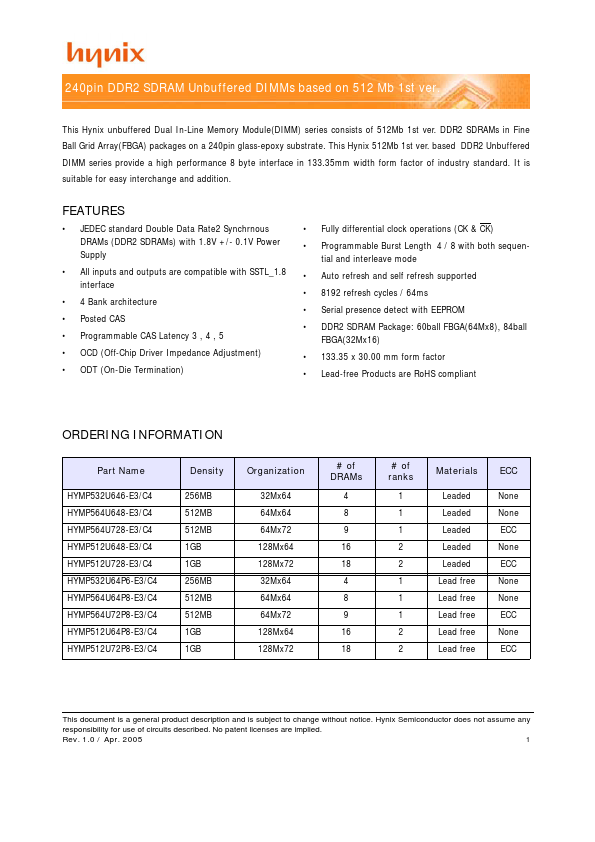

Ddr2 sdram unbuffered dimms based on 512m.

240pin DDR2 SDRAM Unbuffered DIMMs based on 512 Mb 1st ver. This Hynix unbuffered Dual In-Line Memory Module(DIMM) series consists of 512Mb 1st ver. D.