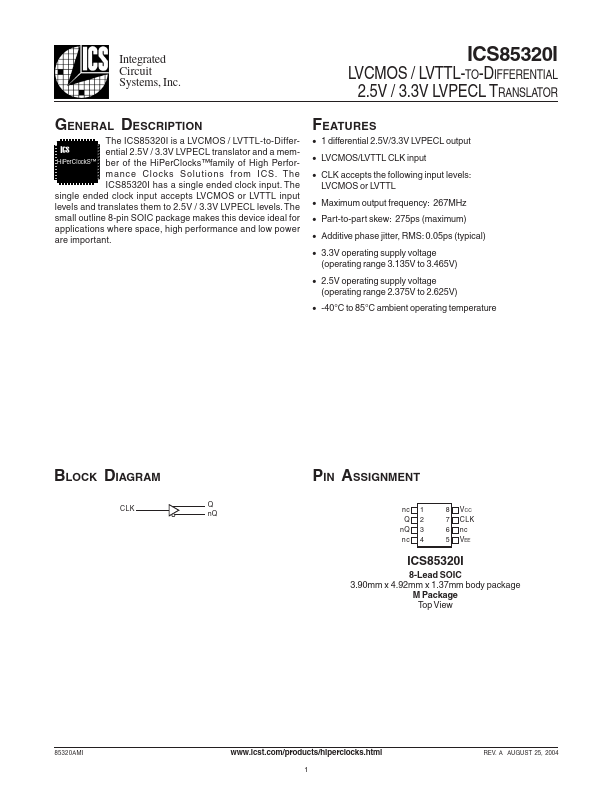

- Part: ICS85320I

- Description: LVPECL TRANSLATOR

- Manufacturer: ICST

- Size: 223.52 KB

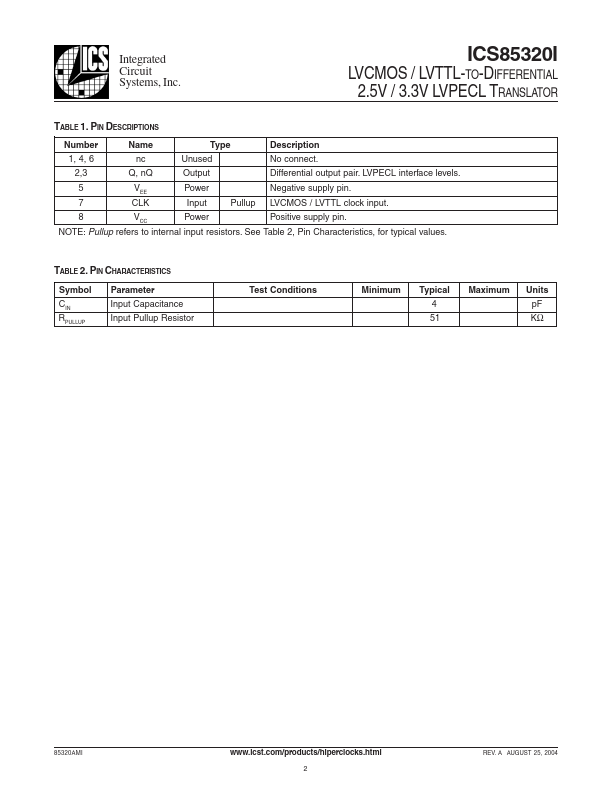

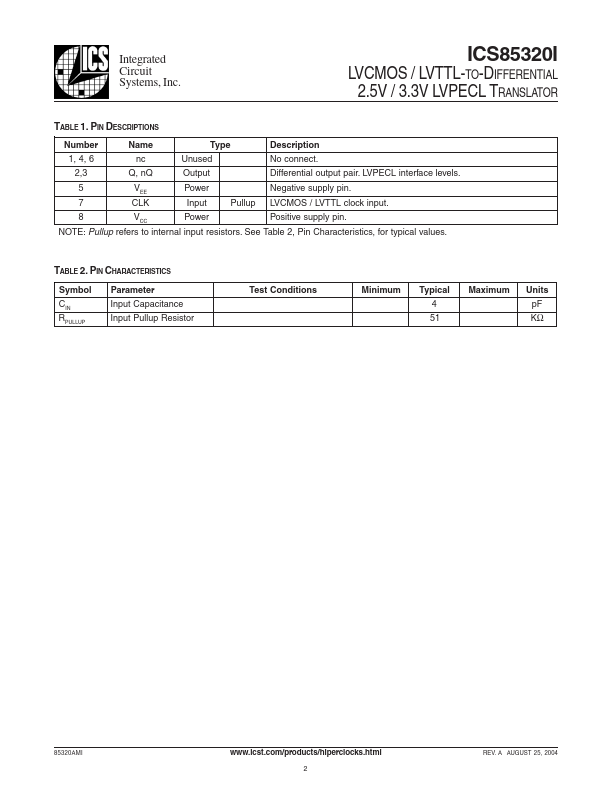

Page 2

Page 2

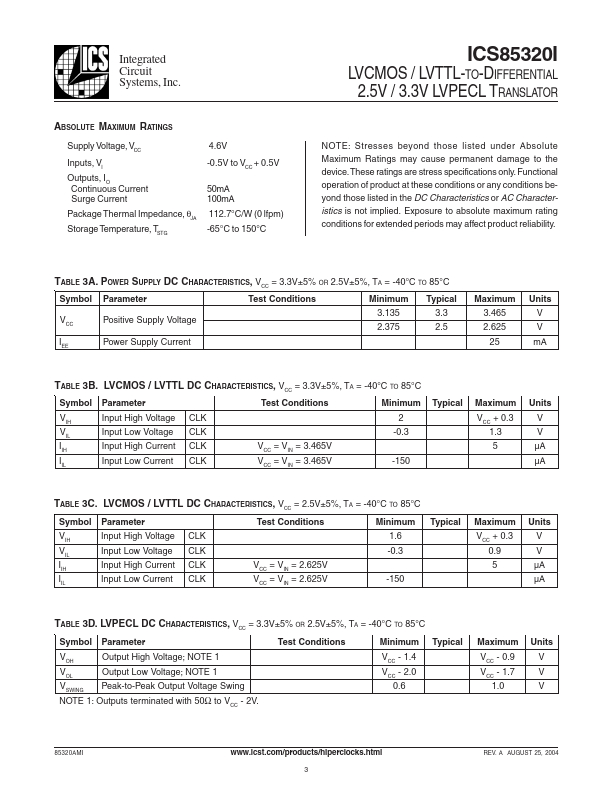

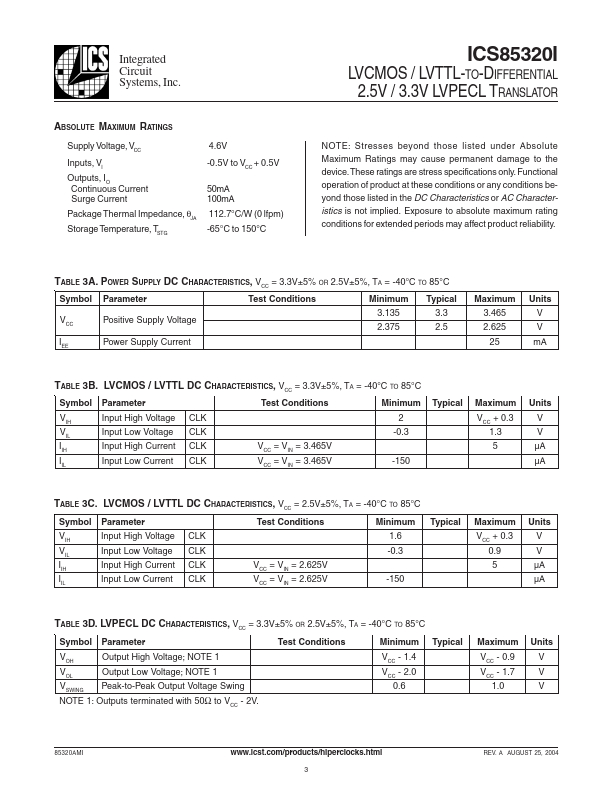

Page 3

Page 3

ICS85320I Key Features

- 1 differential 2.5V/3.3V LVPECL output

- LVCMOS/LVTTL CLK input

- CLK accepts the following input levels: LVCMOS or LVTTL

- Maximum output frequency: 267MHz

- Part-to-part skew: 275ps (maximum)

- Additive phase jitter, RMS: 0.05ps (typical)

- 3.3V operating supply voltage (operating range 3.135V to 3.465V)

- 2.5V operating supply voltage (operating range 2.375V to 2.625V)

- 40°C to 85°C ambient operating temperature