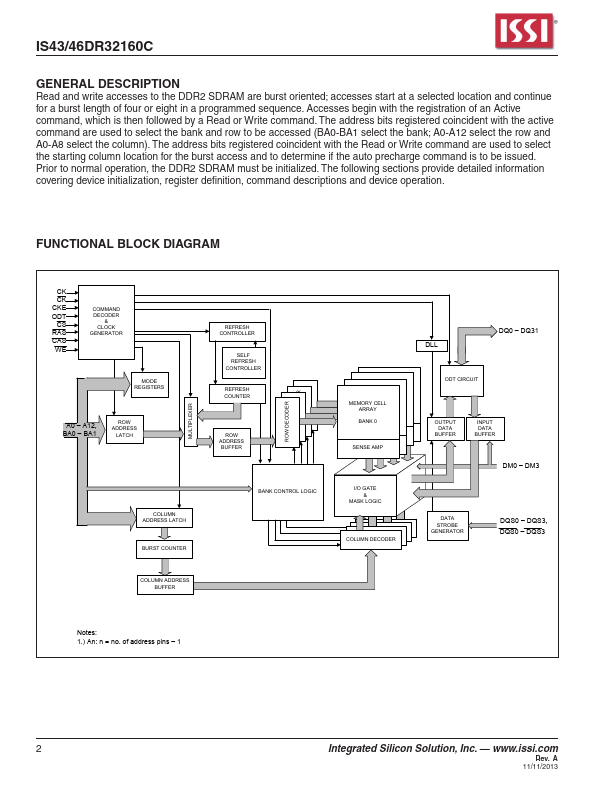

IS43DR32160C Description

ISSI's 512Mb DDR2 SDRAM uses a double-data-rate architecture to achieve high-speed operation. The double-data rate architecture is essentially a 4n-prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O balls. The 512Mb DDR2 SDRAM is provided in a wide bus x32 format, designed to offer a smaller footprint and support pact designs.

IS43DR32160C Key Features

- Vdd = 1.8V ±0.1V, Vddq = 1.8V ±0.1V

- JEDEC standard 1.8V I/O (SSTL_18-patible)

- Double data rate interface: two data transfers per clock cycle

- Differential data strobe (DQS, DQS)

- 4-bit prefetch architecture

- On chip DLL to align DQ and DQS transitions with CK

- 4 internal banks for concurrent operation

- Programmable CAS latency (CL) 3, 4, 5, and 6 supported

- Posted CAS and programmable additive latency (AL) 0, 1, 2, 3, 4, and 5 supported

- WRITE latency = READ latency