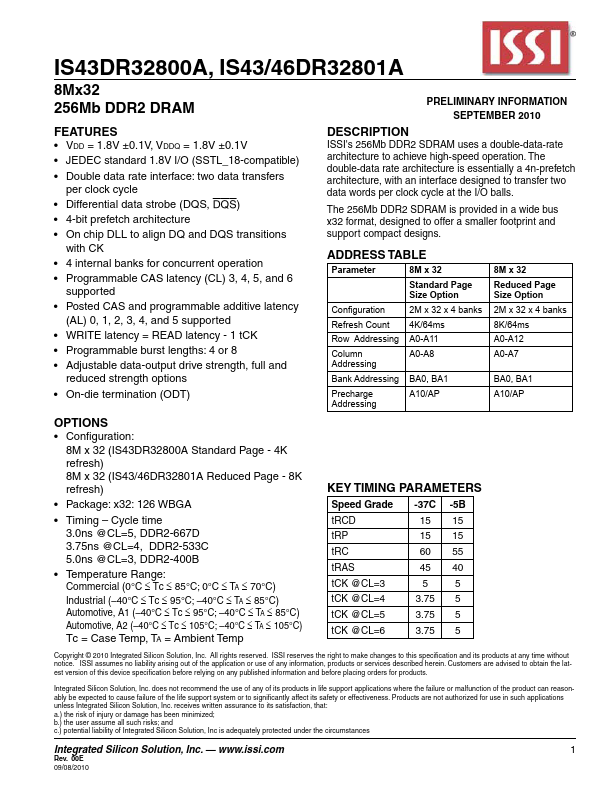

| Part | IS43DR32801A |

|---|---|

| Description | 8Mx32 256Mb DDR2 DRAM |

| Manufacturer | ISSI |

| Size | 625.37 KB |

Pricing from 27 USD, available from ICPartonline and Antdic Electronics.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| ICPartonline | 23577 | 1+ : 27 USD 10+ : 25.65 USD 100+ : 24.3 USD 1000+ : 22.95 USD |

View Offer |

| Antdic Electronics | 22853 | 1+ : 23 USD 10+ : 21.85 USD 100+ : 20.7 USD 1000+ : 18.4 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HM4864-2 | Hitachi Semiconductor | 65536 x 1-Bit DRAM |

| M12L128324A-6BIG2C | Elite Semiconductor Microelectronics Technology | 1M x 32 Bit x 4 Banks Synchronous DRAM |

| A3R12E40CBF | Zentel | 512Mb DDRII Synchronous DRAM |