IS61NVF25672

IS61NVF25672 is STATE BUS SRAM manufactured by ISSI.

- Part of the IS61NVF102418 comparator family.

- Part of the IS61NVF102418 comparator family.

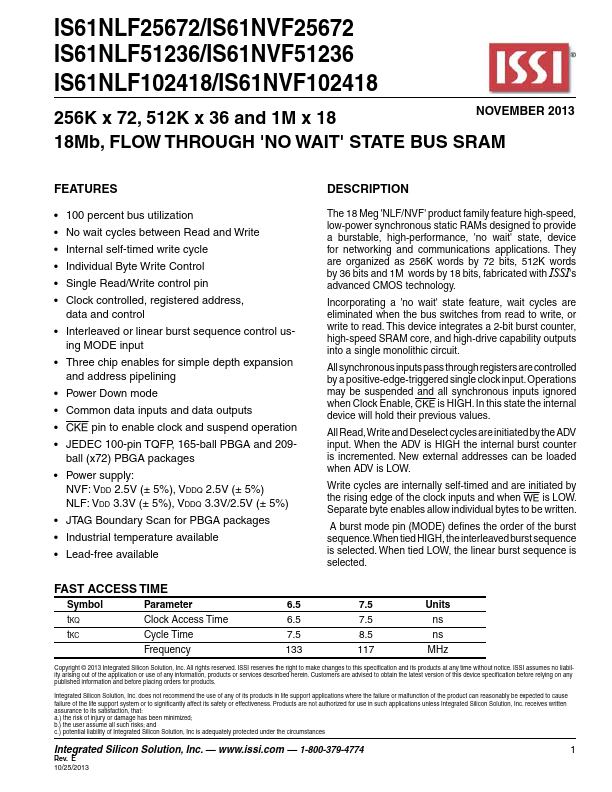

IS61NLF25672/IS61NVF25672 IS61NLF51236/IS61NVF51236

IS61NLF102418/IS61NVF102418

256K x 72, 512K x 36 and 1M x 18

NOVEMBER 2013

18Mb, FLOW THROUGH 'NO WAIT' STATE BUS SRAM

Features

DESCRIPTION

- 100 percent bus utilization

- No wait cycles between Read and Write

- Internal self-timed write cycle

- Individual Byte Write Control

- Single Read/Write control pin

- Clock controlled, registered address, data and control

- Interleaved or linear burst sequence control us- ing MODE input

- Three chip enables for simple depth expansion and address pipelining

- Power Down mode

- mon data inputs and data outputs

- CKE pin to enable clock and suspend operation

- JEDEC 100-pin TQFP, 165-ball PBGA and 209- ball (x72) PBGA packages

- Power supply:

NVF: Vdd 2.5V (± 5%), Vddq 2.5V (± 5%) NLF: Vdd 3.3V (± 5%), Vddq 3.3V/2.5V (± 5%)

- JTAG Boundary Scan for PBGA packages

- Industrial temperature available

- Lead-free available

The 18 Meg 'NLF/NVF' product family feature high-speed, low-power synchronous static RAMs designed to provide a burstable, high-performance, 'no wait' state, device for networking and munications applications. They are organized as 256K words by 72 bits, 512K words by 36 bits and 1M words by 18 bits, fabricated with ISSI's advanced CMOS technology.

Incorporating a 'no wait' state feature, wait cycles are eliminated when the bus switches from read to write, or write to read. This device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit.

All synchronous inputs pass through registers are controlled by a positive-edge-triggered single clock input. Operations may be suspended and all synchronous inputs ignored when Clock Enable, CKE is HIGH. In this state the internal device will hold their previous values.

All Read, Write and Deselect cycles are initiated by the ADV input. When the ADV is HIGH the internal burst counter is incremented. New external addresses can be loaded when...