IC42S32202 Description

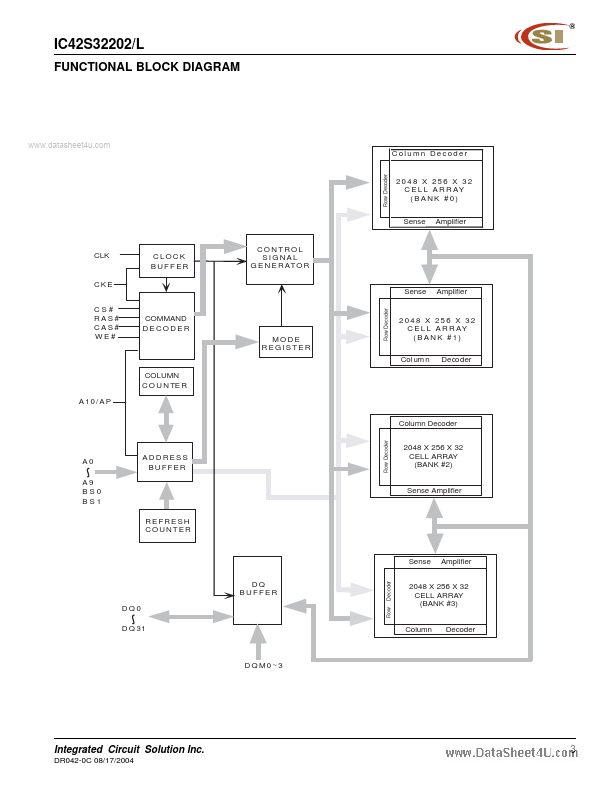

The ICSI IC42S32202 and IC42S32202L is a high-speed CMOS configured as a quad 512K x 32 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal,CLK). Each of the 512K x 32 bit banks is organized as 2048 rows by 256 columns by 32 bits.Read and write accesses start at a selected locations in a programmed sequence. Accesses begin with the registration of a BankActive mand...

IC42S32202 Key Features

- Concurrent auto .. precharge

- Clock rate:166/143/125 MHz

- Fully synchronous operation

- Internal pipelined architecture

- Four internal banks (512K x 32bit x 4bank)

- Programmable Mode -CAS#Latency:2 or 3 -Burst Length:1,2,4,8,or full page -Burst Type:interleaved or linear burst -Burst-

- Burst stop function

- Individual byte controlled by DQM0-3

- Auto Refresh and Self Refresh

- 4096 refresh cycles/64ms