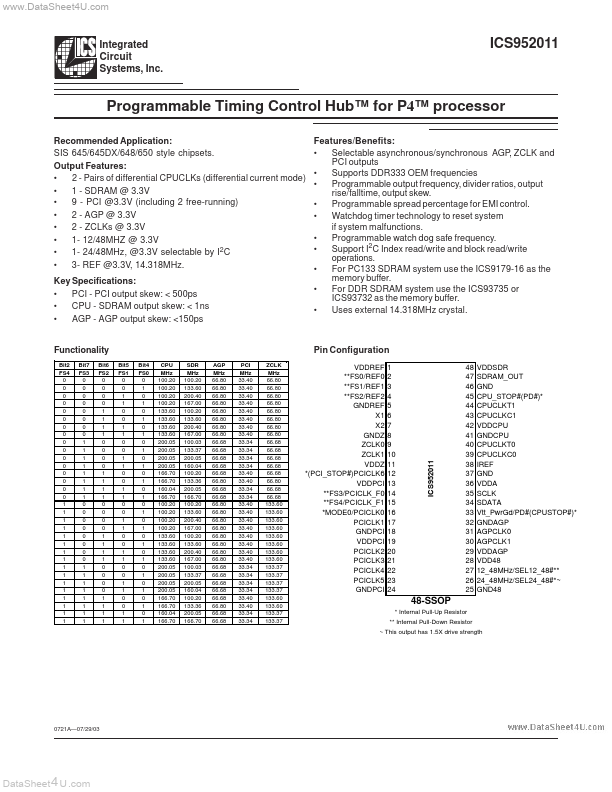

ICS952011

Key Features

- 2 - Pairs of differential CPUCLKs (differential current mode)

- 1 - SDRAM @ 3.3V

- 9 - PCI @3.3V (including 2 free-running)

- 2 - AGP @ 3.3V

- 2 - ZCLKs @ 3.3V

- 1- 12/48MHZ @ 3.3V

- 1- 24/48MHz, @3.3V selectable by I2C

- 3- REF @3.3V, 14.318MHz. Key Specifications:

- PCI - PCI output skew: < 500ps

- CPU - SDRAM output skew: < 1ns